HEWLETT-PACKARD

# Assembly Language I/O Reference Manual

HP-83/85

$$Z = \begin{bmatrix} 10 & 00 \\ 01 & 00 \\ 00 & V_{11} V_{12} \\ 00 & V_{21} V_{22} \end{bmatrix} = \begin{bmatrix} 1 & 0 \\ 0 & V \end{bmatrix}$$

$$X = (A^T A)^{-1} A^T B$$

$$A = \begin{bmatrix} 0 & & & & \\ & 0.8560 & 0.8348 & 0.2327 \\ & 0.0080 & 0.7610 & 1.0505 \\ & 0.0 & 0.0369 & 0.2520 \\ & 0.0 & -0.4688 & -0.5963 \end{bmatrix}$$

$$K = \begin{bmatrix} -0.0709 & 0.1861 & -0.8383 & -0.4806 & 0.1632 \\ 0.0726 & -0.4109 & -0.5354 & 0.7253 & -0.1144 \\ -0.2002 & -0.6231 & 0.1027 & -0.1411 & 0.7357 \end{bmatrix}$$

$$R = \begin{bmatrix} 1.4446 & 1.6867 & 1.2530 \\ 0.0 & -1.3389 & -0.1486 \end{bmatrix}$$

Assembly Language

I/O Reference Manual

HP-83/85

November 1982

Reorder Number

00085-90818

Printed In U.S.A.

©Hewlett-Packard Company 1982

## CONTENTS

---

| Section                                                           | Page |

|-------------------------------------------------------------------|------|

| I INTRODUCTION                                                    |      |

| 1.1 Overview of Low-Level I/O .....                               | 1-1  |

| 1.2 Interface Functional Description .....                        | 1-2  |

| 1.3 Interpreting the Translator Bytes .....                       | 1-3  |

| 1.4 RAM Hooks Available to the I/O Programmer.....                | 1-7  |

| 1.4.1 IRQ20 (102470) .....                                        | 1-7  |

| 1.4.2 IOSP (102407) .....                                         | 1-12 |

| 1.4.3 NEWIRQ .....                                                | 1-14 |

| II I/O PROCESSOR COMMANDS AND PROTOCOL                            |      |

| 2.1 Communications Protocol Between the CPU and the IOP .....     | 2-1  |

| 2.2 Command Protocol Flowcharts .....                             | 2-3  |

| 2.3 I/O Processor Commands .....                                  | 2-9  |

| 2.3.1 Read Status 0 0 0 0 .....                                   | 2-9  |

| 2.3.2 Input 0 0 0 1 .....                                         | 2-9  |

| 2.3.3 Burst I/O 0 0 1 0 .....                                     | 2-10 |

| 2.3.4 Interrupt Control 0 0 1 1 .....                             | 2-10 |

| 2.3.5 Interface Control 0 1 0 0 .....                             | 2-11 |

| 2.3.6 Read Auxiliary 0 1 1 1 .....                                | 2-11 |

| 2.3.7 Write Control 1 0 0 .....                                   | 2-11 |

| 2.3.8 Output 1 0 1 0 .....                                        | 2-12 |

| 2.3.9 Send Commands 1 0 1 1 .....                                 | 2-12 |

| 2.3.10 Write Auxiliary 1 1 1 0 .....                              | 2-12 |

| 2.4 What Happens When the I/O Processor Interrupts the CPU? ..... | 2-13 |

| III PERFORMING I/O OPERATIONS                                     |      |

| 3.1 Introduction .....                                            | 3-1  |

| 3.2 I/O Operation Flowcharts .....                                | 3-1  |

| 3.3 I/O Operations: Utilities and Sample Code .....               | 3-13 |

| 3.3.1 Register Conventions .....                                  | 3-13 |

| 3.3.2 Interrupting Versus Noninterrupting IOP Commands .....      | 3-13 |

| 3.4 Definition of an I/O Operation .....                          | 3-14 |

| 3.4.1 Command Handshaking Utility Subroutines .....               | 3-15 |

| 3.4.2 Status and Control Operations .....                         | 3-18 |

|        |                                                            |      |

|--------|------------------------------------------------------------|------|

| 3.4.3  | Status and Control Utility Subroutines .....               | 3-19 |

| 3.4.4  | Special Control Operations Not Available With BASIC .....  | 3-20 |

| 3.4.5  | Simple Input/Output .....                                  | 3-22 |

| 3.4.6  | Simple Input and Simple Output Utility Subroutines .....   | 3-27 |

| 3.4.7  | Primary Addressing and HP-IB Interface Messages .....      | 3-28 |

| 3.4.8  | Primary Addressing and Interface Message Subroutines ..... | 3-30 |

| 3.4.9  | Miscellaneous I/O Utilities .....                          | 3-32 |

| 3.4.10 | Burst Input/Output .....                                   | 3-34 |

| 3.4.11 | Burst-In and Burst-Out Utility Subroutines .....           | 3-37 |

| 3.4.12 | Burst Command Protocol .....                               | 3-39 |

| 3.4.13 | Burst Execution Speed .....                                | 3-40 |

| 3.4.14 | Interrupting Operations .....                              | 3-40 |

| 3.4.15 | Simulation of I/O ROM Statements .....                     | 3-48 |

| 3.4.16 | Timing Methodology .....                                   | 3-52 |

#### IV SAMPLE CODE

|     |                    |     |

|-----|--------------------|-----|

| 4.1 | Introduction ..... | 4-1 |

| 4.2 | Keywords .....     | 4-1 |

## ILLUSTRATIONS

---

| Figure | Title                             | Page |

|--------|-----------------------------------|------|

| 1-1    | I/O Hardware Diagram .....        | 1-3  |

| 1-2    | Calculator Control Register ..... | 1-4  |

| 1-3    | Processor Status Register .....   | 1-5  |

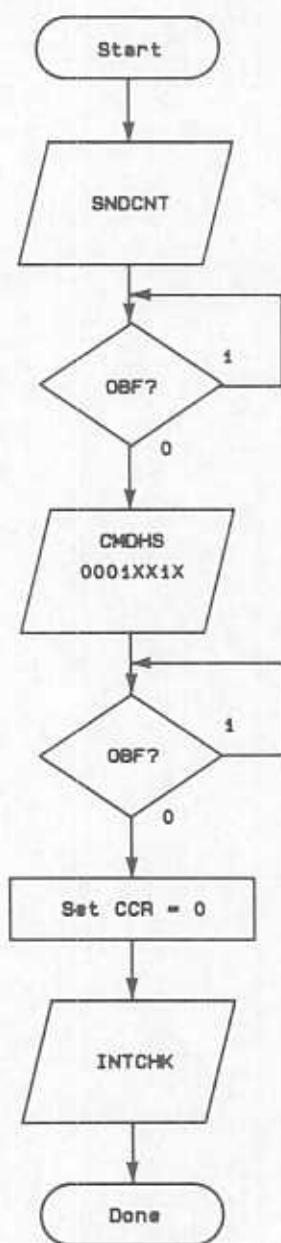

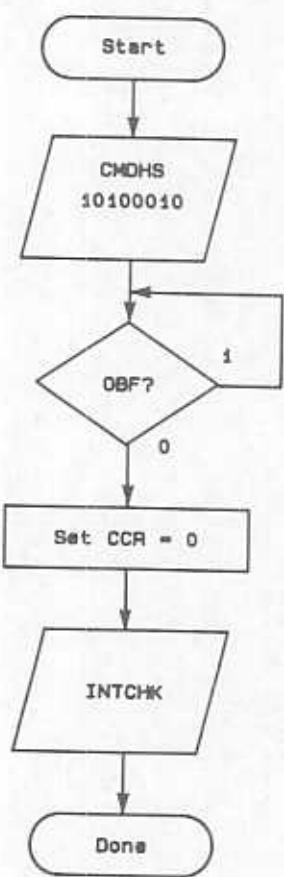

| 2-1    | Reset One IOP .....               | 2-3  |

| 2-2    | Command Handshake .....           | 2-4  |

| 2-3    | Revive An Interrupted IOP .....   | 2-5  |

| 2-4    | Interrupt Service Routine .....   | 2-6  |

| 2-5    | Interrupt Output .....            | 2-7  |

| 2-6    | Interrupt Input .....             | 2-8  |

| 3-1    | Read Status .....                 | 3-2  |

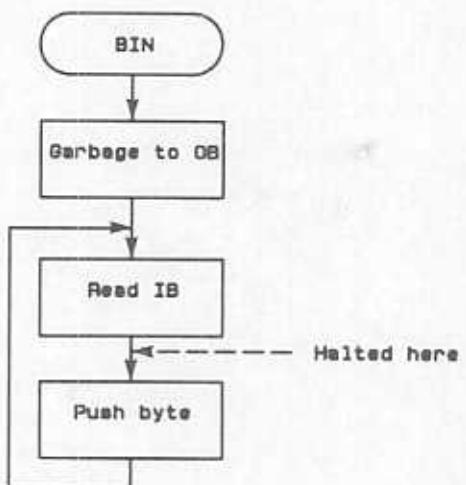

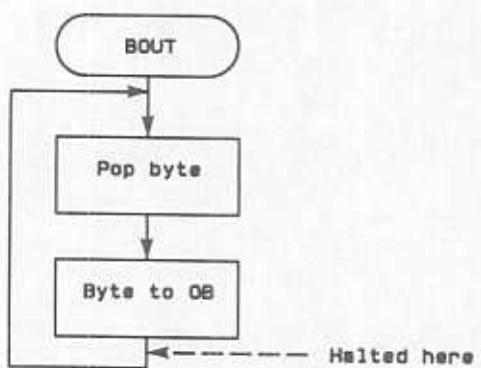

| 3-2    | Simple Input .....                | 3-3  |

| 3-3    | Burst I/O .....                   | 3-4  |

| 3-4    | Burst Loops .....                 | 3-5  |

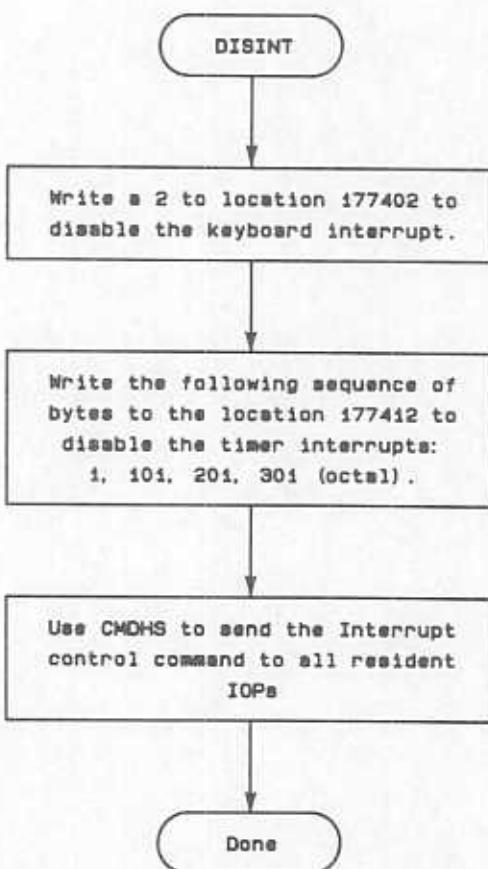

| 3-5    | Disable All Interrupts .....      | 3-6  |

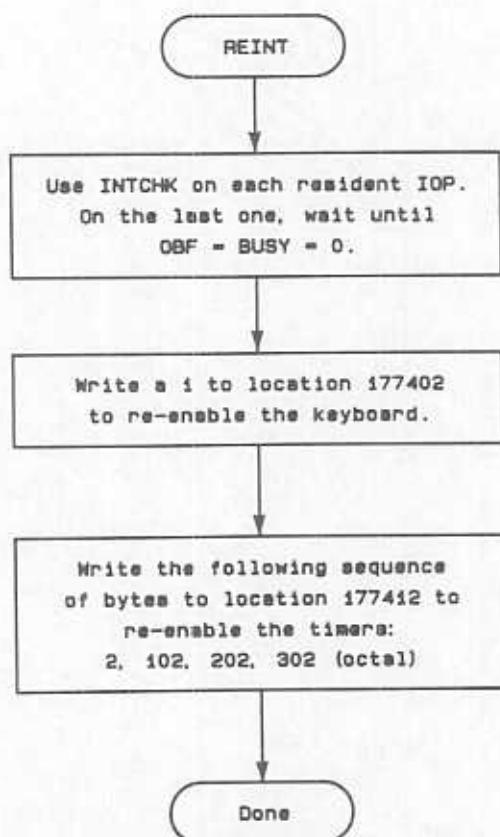

| 3-6    | Re-enable All Interrupts .....    | 3-7  |

| 3-7    | Write Control .....               | 3-8  |

| 3-8    | Initiate Interrupt Input .....    | 3-9  |

| 3-9    | Initiate Interrupt Output .....   | 3-10 |

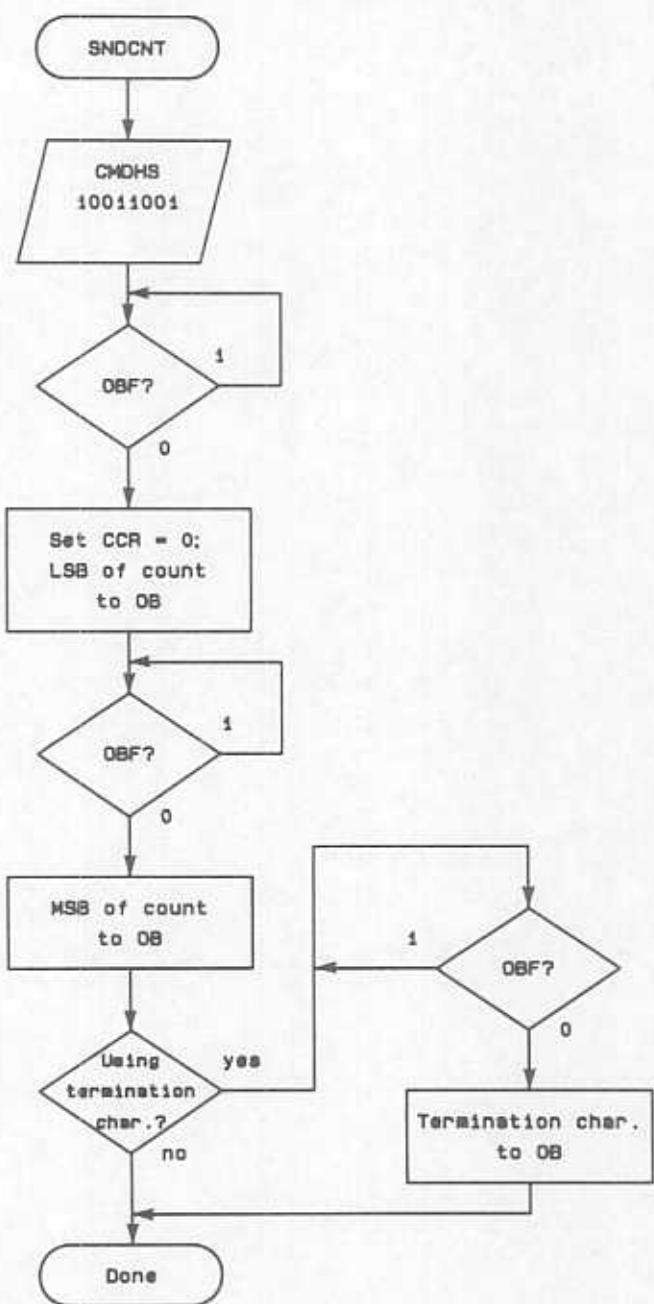

| 3-10   | Send Byte Count .....             | 3-11 |

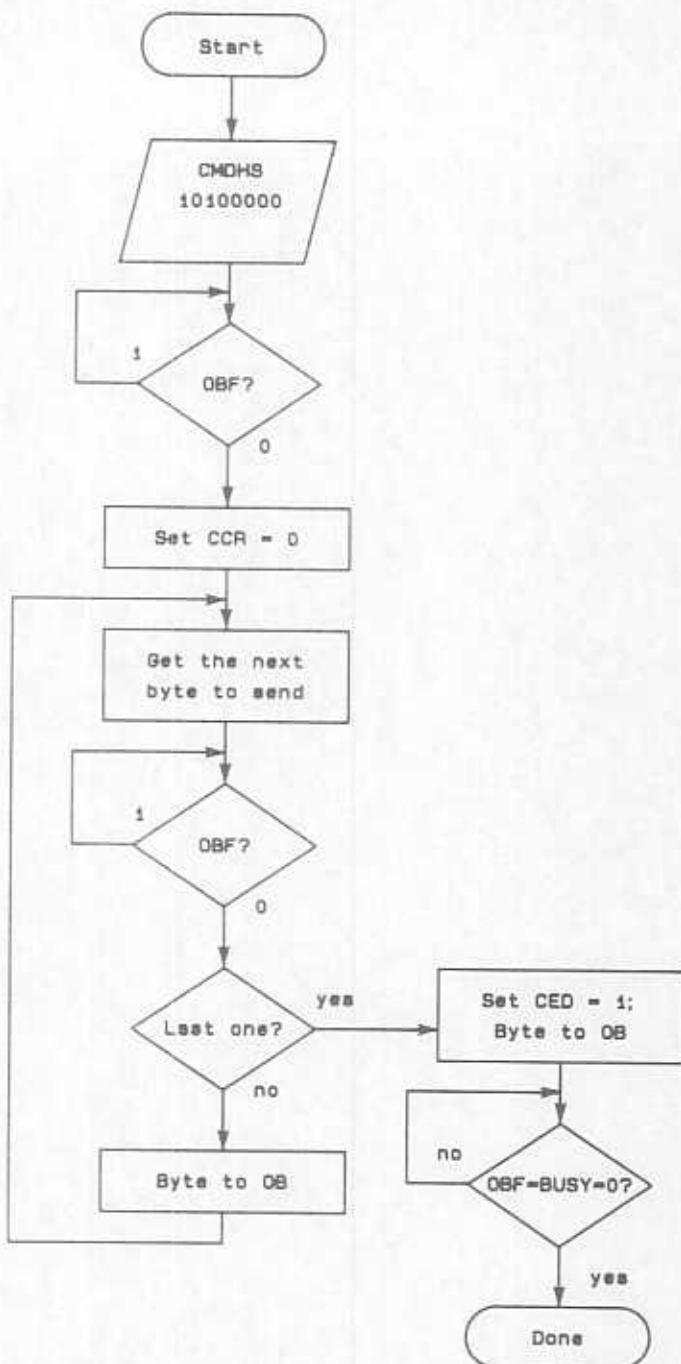

| 3-11   | Simple Output .....               | 3-12 |

## TABLES

---

| Table | Title                                                | Page |

|-------|------------------------------------------------------|------|

| 1-1   | Translator Addressing .....                          | 1-6  |

| 1-2   | Select Code Byte Interpretation .....                | 1-8  |

| 2-1   | Command Bytes .....                                  | 2-2  |

| 2-2   | Interface Control Fields .....                       | 2-11 |

| 2-3   | IOP Interrupt Byte .....                             | 2-13 |

| 3-1   | Execution Times (milliseconds) .....                 | 3-18 |

| 3-2   | Execution Times .....                                | 3-31 |

| 3-3   | Execution Times for HP-IB Interface Operations ..... | 3-34 |

## INTRODUCTION

---

### 1.1 Overview of Low-Level I/O

The purpose of this manual is to document HP-83/85 input/output operations. For example, you may need to speed up a specific data transfer, or do a custom I/O operation. These are problems that cannot be solved with a BASIC program and an I/O ROM. This manual should be used with the Assembler ROM manual (your reference for writing binary programs).

This documentation is arranged in the following sections:

Section I. Introduction--Read this section first. It is an overview of how I/O is used on the HP-83/85.

Section II. I/O Processor Commands and Protocol--Use as a reference for the commands that communicate with the I/O processor on each interface card, and the protocol for communications in this multi-processor system. You will find a flowchart outlining the protocol required to pass a command to the I/O processor. Refer back to this section after you analyze your I/O operation using section 3.

Section III. Performing I/O Operations--Each I/O operation is discussed along with the programming steps required for execution. You will find a detailed discussion of simple input/output operations, burst input/output, interrupt operations, and status and control operations. Documentation on the fastest rates possible to do I/O operations for each interface is included, as well as sample I/O utilities.

Section IV. A Sample Program--This example contains simple, burst, and interrupt transfer routines. It also includes a hardware vector hook interrupt service routine, and other general purpose utilities such as a variable set-up utility.

If you are trying to speed up an I/O operation, you should first make sure the computer is capable of attaining your speed requirements. To do this, compare your requirements with the rates documented in section 3.

## Section 1: Introduction

A tradeoff of speed is required to gain the power of using BASIC with the I/O ROM. The more general your application, the more speed you will gain using binary code. For example, if you are doing a SIMPLE ENTER from a GPIO interface at select code 4 (ENTER 4 in BASIC), you can write a binary program that sends a SIMPLE INPUT command and handshakes each byte into a string variable until the GPIO device is out of data or the string is full. This program bypasses the extra image checking, data formatting, and other options that the I/O ROM allows, making execution at least three times faster.

Once you have determined the feasibility of your requirements, use the following guidelines:

1. Read section 1.

2. Refer to the appropriate flowchart and sample code in section 3.

3. Use section 2 as a reference for commands and protocol.

4. Design a program using the example in section 4.

5. Code and debug your program.

### 1.2 Interface Functional Description

The purpose of interface operations is to transfer data between computer memory and some other device or devices. The source or destination of the data may be a data storage area (buffer) in RAM or direct program interaction.

Interface devices use a variety of methods to communicate. Different interfaces are available with selectable options to allow customizing to a specific method of communication.

Between the interface and the computer, every attempt has been made to have only one method of communication. The only difference between interfaces (as seen by the HP-83/85 low level code) is their respective interface select code numbers which do not affect interface type. Even though different interfaces have different capabilities, they all speak the same language. For example, consider the statement:

```

OUTPUT 5 ; "1"

```

If there is a serial interface at select code 5, then the ASCII character "1" will be output serially. If there is a BCD interface at select code 5, then "1" will be output as a BCD digit. In both cases the computer program operations (data values and instructions executed) are identical.

To maintain uniformity there is a microcomputer in each interface. This microcomputer acts as an interpreter able to listen in one language and speak in another.

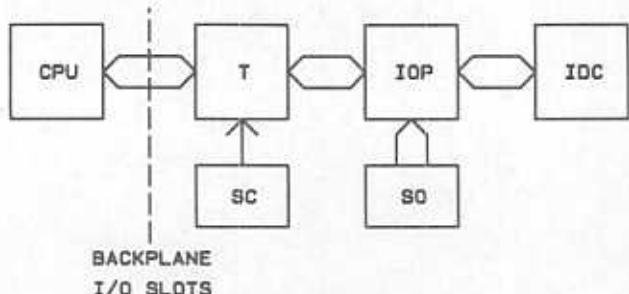

Figure 1-1. I/O Hardware Diagram

The CPU is the central processing unit which executes machine language instructions (either SYSTEM/BASIC or ROM/BINARY). It has unique designations of logic levels, timing, etc. Terminology used in the above diagram and throughout this manual includes:

**Input/Output Processor (IOP):** An 8049 microcomputer which executes preprogrammed microcode. This code allows the processor to converse through interface dependent circuitry (IDC) according to the selected options (SO).

**Translator (T):** A two-byte wide channel with HP-83/85 logic levels, timing, and control on one side and 8049 logic levels, timing, and control on the other side.

**Select Code (SC):** Indicates to the translator where to appear in memory address space.

### 1.3 Interpreting the Translator Bytes

As an I/O programmer, the only access you have to the I/O processor is through the translator. Each translator appears as two consecutive bytes in memory. The I/O processor also sees two bytes. These are full duplex bytes. Unlike memory bytes, what you read from these two bytes is not what you just wrote there. What you read is what the I/O processor wrote into them (with the exception of two control bits). What you write to these bytes is what the I/O processor receives next time it reads them (with the same exception).

## Section 1: Introduction

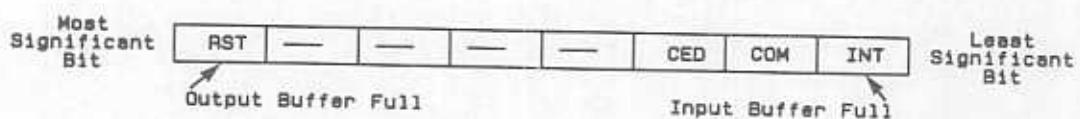

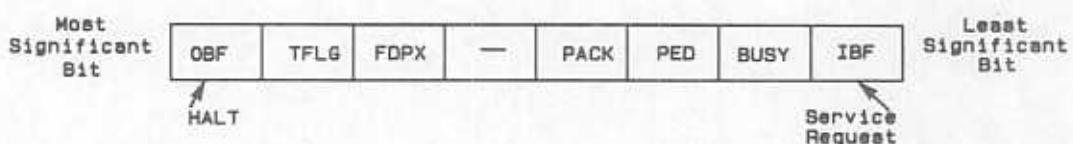

Because of this read and write process, four names are associated with these two bytes. The first byte (lower, even address) is called the calculator control register (CCR) when you write to it and the processor status register (PSR) when you read from it. In general, "calculator" refers to the computer CPU, and "processor" refers to the I/O processor. The second byte (higher, odd address) is called the output buffer (OB) when written to, and input buffer (IB) when read from.

Figure 1-2. Calculator Control Register

RST (reset): When set, the I/O processor initiates the reset operation.

CED (calculator end data): When set, the CED bit indicates to the I/O processor that the computer has declared the current data byte to be the last of the current sequence.

COM (command): This bit tells the I/O processor to interpret the byte it finds in the output buffer. If the COM bit is set then the output buffer contains a protocol command. If the COM bit is clear, then the output buffer contains a byte of data.

INT (interrupt): Setting INT interrupts the I/O processor.

Figure 1-3. Processor Status Register

OBF (output buffer full): Writing a byte to the output buffer sets OBF. It is cleared when the I/O processor reads the output buffer.

TFLG (transfer flag): There are times when more than one byte can be transferred during a single interrupt (for example, with a multi-digit BCD field). When TFLG is set it indicates that the I/O processor has or wants additional bytes.

FDPX (full duplex): When set, FDPX indicates that this I/O processor can do interrupt transfers in both directions concurrently.

PACK (processor acknowledge): This bit is set to confirm that the CPU has interrupted the I/O processor.

PED (processor end data): When set, PED indicates to the computer that the current byte is to be the last of the current input sequence.

BUSY (not idle): When set, BUSY indicates that the I/O processor is occupied.

IBF (input buffer full): IBF is set when the I/O processor writes a byte to the input buffer and is cleared when the CPU reads the input buffer.

The input and output buffers are both eight-bit bytes. The meaning of the bits is entirely situation dependent. For the CCR/PSR, six of the bits are read by the I/O processor as what was written there. What you read is what the I/O processor wrote there. The highest and lowest order bits are control bits. They are read like this:

1. When the I/O processor reads the RST bit, it receives output buffer full.

2. When the I/O processor reads the INT bit, it receives input buffer full.

3. Where you read output buffer full, the I/O processor writes HALT.

4. Where you read input buffer full, the I/O processor writes SRQ (interrupt).

## Section 1: Introduction

The translators are positioned in address space according to the three select code settings as indicated in table 1-1.

Table 1-1. Translator Addressing

| Address | Name    | Switches | Select Code |

|---------|---------|----------|-------------|

| 177520  | CCR/PSR | 0 0 0    | 3           |

| 177521  | OB/IB   |          |             |

| 177522  | CCR/PSR | 0 0 1    | 4           |

| 177523  | OB/IB   |          |             |

| 177524  | CCR/PSR | 0 1 0    | 5           |

| 177525  | OB/IB   |          |             |

| 177526  | CCR/PSR | 0 1 1    | 6           |

| 177527  | OB/IB   |          |             |

| 177530  | CCR/PSR | 1 0 0    | 7           |

| 177531  | OB/IB   |          |             |

| 177532  | CCR/PSR | 1 0 1    | 8           |

| 177533  | OB/IB   |          |             |

| 177534  | CCR/PSR | 1 1 0    | 9           |

| 177535  | OB/IB   |          |             |

| 177536  | CCR/PSR | 1 1 1    | 10          |

| 177537  | OB/IB   |          |             |

These bytes are accessed using instructions such as LD, ST, PU, and PO, with the exception of multi-byte instructions which do not work as expected. If you read from an address which is not claimed by a translator, you will read all 1's. If you write to such an address your data will be lost.

The mapping of select codes into memory space is used by the I/O ROM and the standard I/O interfaces. A similar set of addresses exists from 177500 to 177517. This additional set has some differences which are:

- The I/O ROM does not handle these locations. If an interrupting translator is in one of these locations, the I/O ROM service routine branches to the hook NEWIRQ.

- A factory mask option, rather than a select code switch, causes a translator to occupy this region.

- The locations 177500 and 177501 (which correspond to switch settings of 0 0 0 or select code 3 in this region) are unavailable for a select code because of the global uses of these addresses.

## 1.4 RAM Hooks Available to the I/O Programmer

### 1.4.1 IRQ20 (102470)

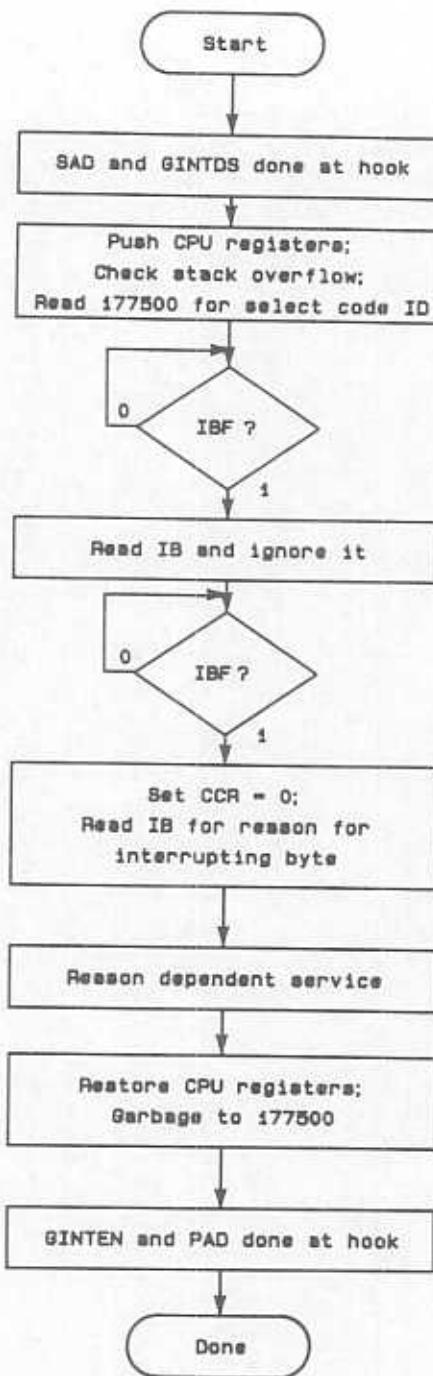

In the system reserved area of RAM memory, IRQ20 is a location that is called when an IOP interrupts the CPU. The system code does not use this hook except to initialize it with a RTN instruction at power-on.

Control passes to IRQ20 when the CPU is interrupted by an IOP. This is how the transition looks at the hardware level:

1. The CPU, rather than executing the next instruction in its normal sequence, pushes the address of that next instruction onto the R6 (return) stack. It then notifies the interrupting device (translator) that it's ready.

2. The translator returns the number 20 (octal) as an interrupt vector for the CPU. Other types of interrupting devices return other vectors.

3. The CPU reads location 20 (in system ROM), gets the address of IRQ20 (which is stored there), and commences execution at IRQ20. Thus, when considering the code for IRQ20 and the interrupt service routine which it calls, the following conditions can be assumed from the fact that the code at IRQ20 is executing: there is a return address on the R6 stack; and the interrupting device is an IOP.

## Section 1: Introduction

In order for the interfaces to function, ROM or binary code must take the hook at IRQ20. The IOPs need interrupt service to complete their power-on reset routines (they must interrupt to report the self-test results). If any one of the three ROMs which use interfaces (I/O, Plotter/Printer, and Mass Storage) is present in the system, this power-on reset protocol will be handled by the ROMs before your binary program is loaded. If none of these three is present, then you must take the IRQ20 hook and complete the reset yourself before you can use the interfaces.

You may do simple I/O without taking IRQ20 if another ROM is handling power-on reset. Also, if the other ROM is the I/O or Mass Storage ROM, then the service routine hooked in IRQ20 by one or the other (I/O if both ROMs are present), will be able to handle your burst termination interrupt and terminate the infinite loop. For all other situations you will want to manage your own interrupt service procedures so you will take the hook at IRQ20.

If you have one of the above ROMs doing the power-on reset, you will miss the opportunity to identify the select codes of all translators present. In this case, load a copy of the byte at 100667 (octal). This is a system location used by these ROMs as a "select code present" indicator. If the bit is set, the select code is there.

Table 1-2. Select Code Byte Interpretation

| MSB | Bit Number  | 7  | 6 | 5 | 4 | 3 | 2 | 1 | 0 | LSB |

|-----|-------------|----|---|---|---|---|---|---|---|-----|

|     | Select Code | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 |     |

If you need to write an interrupt service routine (ISR), the rest of this section provides an explanation of the code required. Following is the code at the hook.

102470 IRQ20 RTN (before the hook is first taken)

Once it's been taken:

```

102470 IRQ20 SAD

102471 STBD R#,GINTDS

102474 JSB =ROMJSB

102477 IRQ20+ DEF ISR

102501 BYT ROM#

102502 STBD R#,GINTEN

102505 IRQPAD PAD

102506 IRQRTN RTN

```

## Section 1: Introduction

Taking the hook at IRQ20 is accomplished by storing the above instructions at IRQ20 (IRQ20+ is a convenience label to allow two multi-byte store operations).

The individual instructions are discussed next. Basically these instructions are the first and the last of your interrupt service routine (ISR). Recall that a proper ISR leaves no trace of its execution as far as the interrupted code is concerned. On the HP-83/85 this means that the ISR must preserve the CPU state, current ROM selection, the CPU registers, and the stacks (R6 and R12).

|                |                                                                                                                                                                                         |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SAD            | Saves the CPU state.                                                                                                                                                                    |

| STBD R#,GINTDS | Assures that the ISR cannot be interrupted.                                                                                                                                             |

| JSB =ROMJSB    | Calling through ROMJSB preserves the current ROM selection.                                                                                                                             |

| DEF ISR        | Address of service routine.                                                                                                                                                             |

| BYT ROM#       | ROM number of service routine (or 0 for binary program ISR).                                                                                                                            |

| STBD R#,GINTEN | Re-enables global interrupts.                                                                                                                                                           |

| PAD            | Restores the CPU state.                                                                                                                                                                 |

| RTN            | Pops the return address off the R6 stack and resumes execution where it was interrupted (except at burst I/O termination where the return address is intentionally altered by the ISR). |

The code at the hook handles preservation of the CPU state and ROM selection. Preservation of the CPU registers and stack conditions is handled by the ISR code. For the CPU registers this amounts to pushing the contents of registers that might be used onto the R6 stack. For stack conditions this amounts to popping them back off before your ISR returns. There is, however, a possibility for stack overflow which must be addressed by the ISR. To understand the problem, we need a picture of the R6 stack from the moment of interrupt to the time when your ISR checks for this condition.

Start with the address pushed by the CPU when it is interrupted. Next, there is a SAD instruction at IRQ20 which pushes the CPU status in three bytes. The jump instruction to ROMJSB saves the return address on the stack. ROMJSB increments this address by three (to step past the DEF ISR and BYT ROM# locations that it uses as the desired JSB target) and then pushes CPU registers R0 and R1, the currently selected ROM number, and its own return address as it jumps (JSB) to the ISR. The first thing the ISR does is to push any CPU registers that it might use.

## Section 1: Introduction

Second, the ISR checks for stack overflow. The R6 stack at the time of the check looks like this:

R6-----

2 bytes      Interrupted return address.

3 bytes      SAD.

2 bytes      IRQ20 return address.

2 bytes      R0 and R1.    \ ROMJSB puts these

1 byte       ROM number.   / 3 bytes on.

2 bytes      ROMJSB return address.

n bytes      Pushed by ISR.

Now go back and look at the last three instructions at the IRQ20 hook:

STBD R#,GINTEN

PAD

RTN

These instructions are executed after the ISR has finished and returned to ROMJSB. At the time of execution the R6 stack appears like this:

R6-----

2 bytes      Interrupted return address.

3 bytes      SAD.

and after the execution of the PAD instruction:

R6-----

2 bytes      Interrupted return address.

and after execution of the RTN instruction:

R6-----

-              Empty, the state before the interrupt.

The problem arises because interrupts are enabled by the STBD R#, GINTEN, but the stack is not empty until after the execution of RTN. If a fast interface is interrupting, the next interrupt will occur while ISR is still busy. As soon as STBD R#,GINTEN is executed, the interrupt will be recognized and PAD will not be executed.

The address will be pushed as the interrupted return address and the stack will look like this at the stack overflow check:

|             |                                   |

|-------------|-----------------------------------|

| 2 bytes     | Real interrupted return address.  |

| 3 bytes     | Real SAD data.                    |

| 2 bytes     | Extra interrupted return address. |

| trouble---- |                                   |

| 3 bytes     | Extra SAD data.                   |

| 2 bytes     |                                   |

| 2 bytes     |                                   |

| 1 byte      | (not changed)                     |

| 2 bytes     |                                   |

| n bytes     |                                   |

R6-----

If the interrupt should occur after the PAD instruction but before the RTN, the stack appears like this:

|             |                                   |

|-------------|-----------------------------------|

| 2 bytes     | Real interrupted return address.  |

| trouble---- |                                   |

| 2 bytes     | Extra interrupted return address. |

| 3 bytes     |                                   |

| 2 bytes     |                                   |

| 2 bytes     |                                   |

| 1 byte      |                                   |

| 2 bytes     |                                   |

| n bytes     |                                   |

R6-----

If there are many fast interrupts, the extra bytes will build up until the stack exceeds the allocated size. The ISR knows how many bytes it pushed for CPU register preservation. It takes a copy of R6 and subtracts this number plus 12 (decimal), from the 12 bytes known to be there from the saving done by the CPU, IRQ20, and ROMJSB. This gives it a pointer to the "interrupted return address" on the R6 stack. To distinguish "real" from "interrupted return address" on the R6 stack. To distinguish "real" from "extra," the ISR compares this address to the two known addresses (102505 and 102506) of the PAD and RTN instructions. The names IRQPAD and IRQRTN will be used to refer to the addresses of these two instructions. If the address found is IRQRTN, the ISR knows that the previous ISR was one instruction short of completion when the current interrupt occurred and that the real address is just in front of the current one.

To fix the problem, the ISR moves the top contents of the R6 stack (the three bytes used by SAD through "n" bytes used by the ISR) down two bytes (eliminating the extra return address to IRQRTN) and decrements R6 by two. Nothing is lost because the return to IRQRTN would simply have executed the RTN instruction there which would have returned to the real address.

If the address found is IRQPAD, the ISR knows that the previous ISR did not execute the PAD instruction, so there are five extra bytes. It moves the stack top contents (starting at the return address for IRQ20 through the bytes occupied by ISR) down five bytes and decrements R6 by five. Again, nothing is lost because the extra SAD data was about to be replaced by the real SAD data when the PAD instruction was interrupted.

You can see that every time the ISR is called for an interrupt, it must clean up the stack if the previous ISR did not.

#### 1.4.2 IOSP (102407)

IOSP is also a location in the RAM system reserved area. The executive loop jumps to IOSP when it gets to the end of a BASIC program line and finds that the service request bit is set (bit 4 in XCOM (R17)) and the I/O interrupt bit is set (bit 1 in the RAM location SVCWRD (100151)). This hook is the means of implementing end-of-line branches. When an end-of-line branch condition is noticed while executing a BASIC line, the type of the condition is stored in RAM. The bits are set in XCOM and SVCWRD and the code goes on executing the current BASIC program line. At the end of the line, the executive loop branches through IOSP to the end-of-line service routine (EOLSV) whose address was set up in the IOSP hook. EOLSV notes the condition and executes the appropriate GOTO or GOSUB.

Note: Use the rest of this section to create an ISR that performs an end-of-line branch.

To take the hook at IOSP, store these instructions at IOSP (102407).

```

102407  IOSP  JSB =ROMJSB

102412      DEF EOLSV

102414      BYT ROM#      (0 for binary programs)

102415      RTN

```

End-of-line branching requires a GOTO or GOSUB as part of the statement that sets it up. The parsing must be done correctly, so let's discuss a sample statement, "ON SELFTEST <select code> GOTO/GOSUB line#." This statement is to set up an end-of-line branch which will be triggered by the select code's IOP interrupting for a self-test report (after being reset). The parse code will be executed when the keyword ON SELFTEST is scanned.

At first things are fairly normal; the instruction PUBD R43,+R6 is used to save the keyword token. The instruction JSB =NUMVA+ is used to parse the select code and then to pop the keyword token back and push it onto the R12 stack with a 370,ROM# or a 371,0.

At this point you must handle the GOTO or GOSUB. NUMVA+ called SCAN before it returned (if you don't have any arguments you must do an explicit call to SCAN in place of NUMVA+) and SCAN left the primary attribute byte of the next token in R47. If R47 contains octal 210, then the next token is a GOTO or GOSUB. If R47 is not 210, you have a syntax error.

Having confirmed the 210 in R47, the parse code executes:

```

JSB =ROMJSB

DEF GOTOSU

BYT 0

GTO ROMRTN

```

GOTOSU is the system routine to parse GOTO/GOSUB and is at DAD 17435. If the syntax is correct, this routine pushes three bytes onto the R12 stack (and thus appends them to the program line being parsed) after the bytes put there by the ON SELFTEST parse code.

The run time code for this keyword token has two tasks. The first is to recover the select code value from R12 and an indicator in RAM. The ISR will then know that a self-test interrupt from this select code is the cause for setting the service request bits (in XCOM and XVCWRD) for an end-of-line branch.

The second task is to set up (but not execute) the GOTO or GOSUB. Taking a look at the compiled BASIC line we see:

| Token for Fetch select code | Token for Execute ON SELFTEST | Token for GOTO/GOSUB line# |

|-----------------------------|-------------------------------|----------------------------|

|-----------------------------|-------------------------------|----------------------------|

When the ON SELFTEST run time code is executed, the BASIC program counter (R10) is pointing to the GOTO/GOSUB token which is a random GOTO/GOSUB token parsed by the system routine GOTOSU. The run time code must store the contents of R10 somewhere in RAM for future use by the end-of-line service routine. The run time code should also increment R10 by three to skip execution of the GOTO/GOSUB when the ON SELFTEST statement is executed.

After execution of the ON SELFTEST statement, the chosen select code interrupts with a self-test report. The ISR, noting that ON SELFTEST is active for that select code, sets an indicator to state that this particular end-of-line branch condition has been met. It then sets the XCOM and SVCWRD bits. Note that the complementary OFF SELFTEST statement needs only to reset the "active" indicator set by the ON SELFTEST statement.

The first thing the end-of-line service routine does is to determine why execution passed to it. Due to the structure of the system's executive loop, the EOLSV routine must interact with the system code in a complex way. You should copy these portions of code from the sample program. The execution of the EOLSV is explained next.

If more than one "on condition" statement is active, the desired statement is selected. When the token from this statement was executed, the GOTO or GOSUB token following it was bypassed, but the R10 BASIC program counter pointing to it was saved. The EOLSV routine now recovers that copy of R10. It stores the current R10 in a system RAM location (100040) called ONFLAG as a return address in case the branch is a GOSUB. It sets CSTAT (R16) to 7 to indicate that a GOTO or GOSUB is taking place as part of the execution of a line. Then it places the recovered pointer into R10 and returns to the executive loop which performs the actual branch. The EOLSV routine keeps the request bits in XCOM and SVCWRD set so that IOSP will be called again. When EOLSV is called again, it then decides whether or not it has finished with end-of-line branching and if it has, the request bits will be cleared.

#### 1.4.3 NEWIRQ

This is a hook provided by the I/O ROM in its stolen RAM at IOBASE plus 630 octal. When the ISR from the I/O ROM gets to the point of reading the address of the interrupting translator's CCR/PSR and the address turns out to be in the lower block of select codes not recognized by the I/O ROM, the ISR (from the I/O ROM) jumps to NEWIRQ. It has already saved everything (including the CPU registers listed below), performed the stack overflow check, and set up three register pairs: R0 and R24 point to the CCR/PSR and R26 points to the OB/IB of the interrupting translator. When the NEWIRQ routine returns through the hook, the ISR restores everything and returns through IRQ20. The hook should be taken with the following code:

```

JSB =ROMJSB

DEF NEWISR

BYT ROM #

RTN

```

The CPU registers saved by the ISR are: R2-3; R14-15; R20-27; R30-37; R40-47; and R60-67.

## I/O PROCESSOR COMMANDS AND PROTOCOL

---

### 2.1 Communications Protocol Between the CPU and the IOP

The way the CPU and the IOP communicate is referred to as IOP protocol. This protocol defines commands and a handshaking system for interfacing at the machine level. The location of the input and output buffers allows transfer of individual bytes between the CPU and the I/O processor. Bytes from the I/O processor to the CPU are always interpreted as data bytes (some of this data is I/O processor status information but there is no indicator bit to flag this; it is a matter of context). Bytes from the CPU to the I/O processor may be either data bytes or command bytes. The I/O processor reads the calculator control register before it reads the output buffer and uses the COM bit to decide if the byte in the output buffer is a data byte or a command byte. If it is a command byte (COM = 1), the I/O processor interprets it according to the protocol command language.

Each command byte is an opcode and a field. The opcodes and their field identifiers are shown in table 2-1.

Table 2-1. Command Bytes

|                      | Opcode (4 Bits) | Field (4 Bits)    |

|----------------------|-----------------|-------------------|

| Most Significant Bit | 0 0 0 0         | Read Status       |

|                      | 0 0 0 1         | Input             |

|                      | 0 0 1 0         | Burst I/O         |

|                      | 0 0 1 1         | Interrupt control |

|                      | 0 1 0 0         | Interface control |

|                      | 0 1 0 1         | (unused)          |

|                      | 0 1 1 0         | (unused)          |

|                      | 0 1 1 1         | Read auxiliary    |

|                      | 1 0 0 -         | Write Control     |

|                      | 1 0 1 0         | Output            |

|                      | 1 0 1 1         | Send              |

|                      | 1 1 0 0         | (unused)          |

|                      | 1 1 0 1         | (unused)          |

|                      | 1 1 1 0         | Write auxiliary   |

|                      | 1 1 1 1         | Extension         |

Of the 16 possible four-bit opcodes, one disappears because opcodes 1 0 0 0 and 1 0 0 1 are really one opcode with a five-bit field. The four unused numbers and "extension" leave 10 opcodes of interest which will be discussed individually. It is conceptually helpful to note that opcodes with the most significant bit set are "wait for data" commands. The first thing the I/O processor has to do after receiving the command is wait for a related data byte from the CPU. The low-numbered opcodes are "immediate execute" commands as they start off by doing something other than wait for the CPU to release a byte.

## 2.2 Command Protocol Flowcharts

The following flowcharts demonstrate the handshaking system used in IOP protocol.

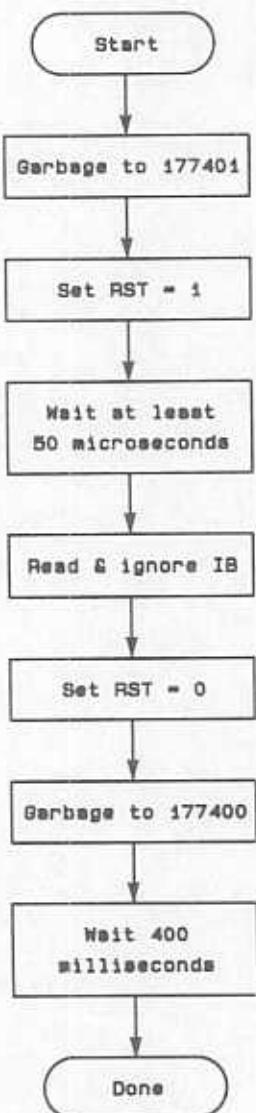

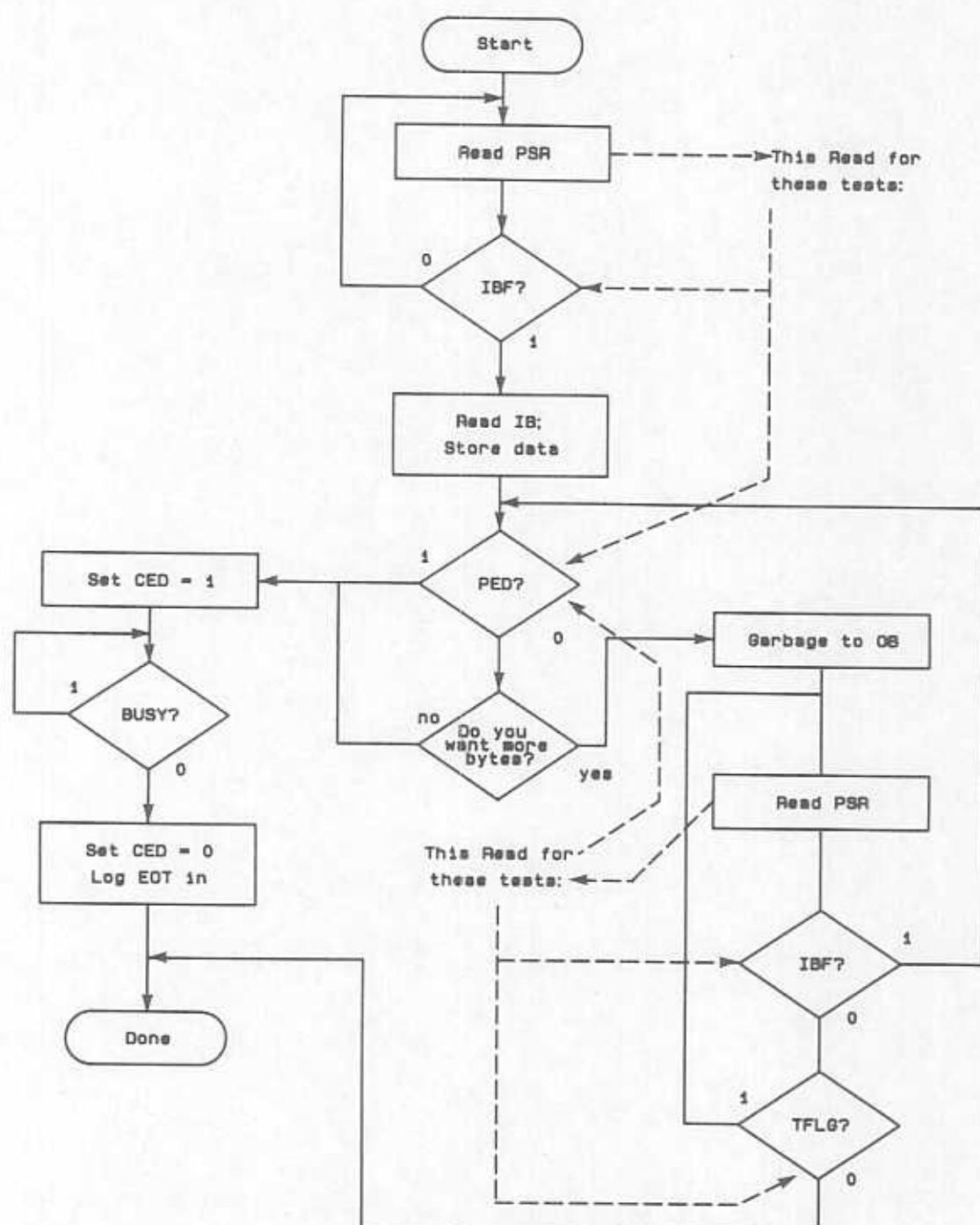

Figure 2-1. Reset One IOP

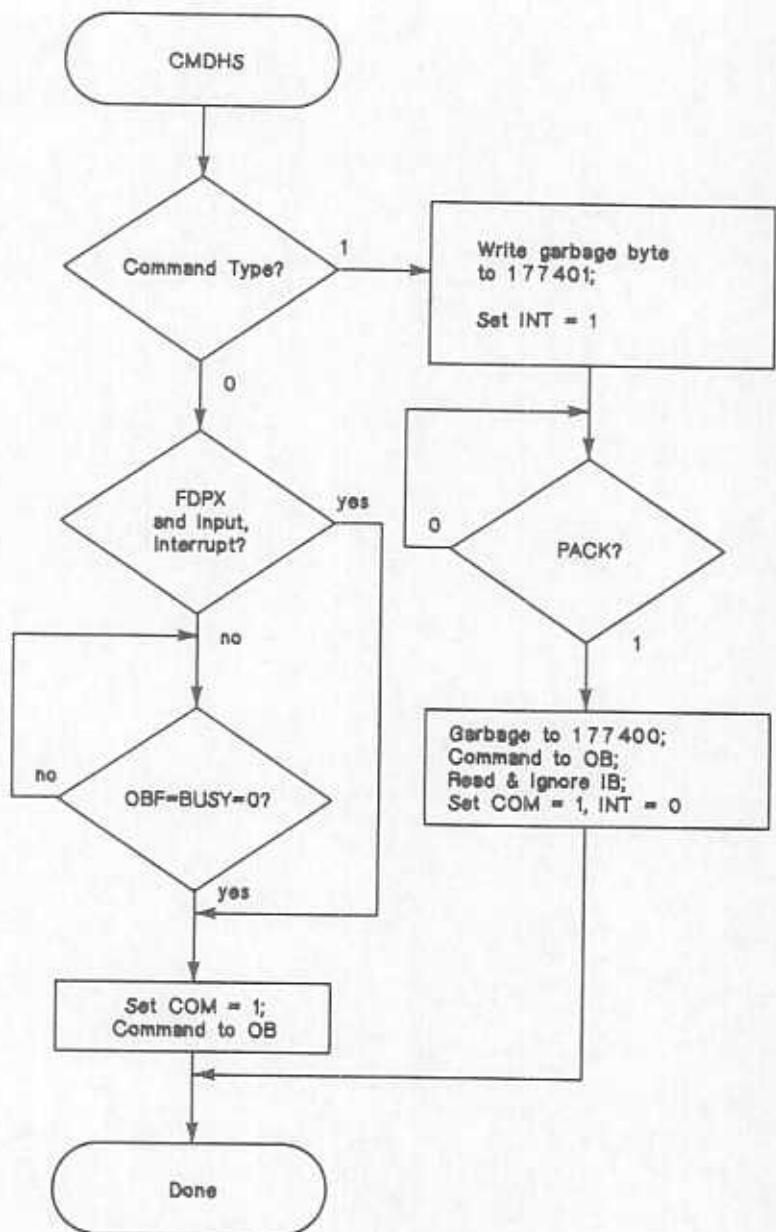

Figure 2-2. Command Handshake

Figure 2-3. Revive An Interrupted IOP

Figure 2-4. Interrupt Service Routine

Figure 2-5. Interrupt Output

Figure 2-6. Interrupt Input

## 2.3 I/O Processor Commands

## 2.3.1 Read Status 0 0 0 0

The four-bit field is the number of the status register to be read first. Successive reads get consecutive registers. This command implements the STATUS statement.

## 2.3.2 Input 0 0 0 1

The field is:

| MSB | Count<br>Term. | Char.<br>Term. | INTR<br>SIMPLE | IOP<br>Term. | LSB |

|-----|----------------|----------------|----------------|--------------|-----|

| 3   | 2              | 1              |                | 0            |     |

This opcode is used for both simple input and interrupt input. If bit 1 is "0," it's a simple input. If bit 1 is "1," it's an interrupt input. Bit 0 set also indicates that the I/O processor should terminate the input if the interface dependent condition is met (EOI). To terminate an input operation the I/O processor sets the PED bit in the processor status register. If the operation is an interrupt input, bits 3 and 2 may be set to enable two other termination criteria. For bit 3 set the I/O processor will terminate the transfer if the number of bytes transferred is equal to the number stored in control registers 25 and 26 (refer to opcode 1 0 0). For bit 2 set the IOP will terminate the transfer upon receipt of a byte equal to the one stored in control register 27 (refer to opcode 1 0 0). The CPU may terminate the input operation by setting CED = 1.

In fact, the CPU must set CED = 1 if PED = 1. Between the time that the command is received and some termination takes place the I/O processor fetches bytes from the I/O device and sends them to the CPU. For simple input, it does so by putting them into the input buffer because the CPU is waiting to take them out. For an interrupt input, the I/O processor interrupts the CPU with the reason for interrupting being the availability of one or more bytes for transfer in.

## 2.3.3 Burst I/O 0 0 1 0

The field is:

| MSB | 0 | IOP<br>TERM | EOL<br>OUT | INPUT<br>OUTPUT | LSB |

|-----|---|-------------|------------|-----------------|-----|

|     | 3 | 2           | 1          | 0               |     |

This opcode is for burst I/O, both input and output. Bit 0 indicates input ("1") or output ("0"). If it is an output, setting bit 1 will cause the I/O processor's programmed EOL sequence to be sent out at the end of the transfer (otherwise the interface EOI condition will be asserted with the last byte). If the operation is an input, clearing bit 2 allows the I/O processor to terminate the burst if its EOI termination condition is met. The CPU must always give the IOP a byte count (control registers 25 and 26) before a burst operation. After giving the burst command, the CPU enters a very tight infinite loop to transfer data as fast as it can. This burst is always terminated by the I/O processor which interrupts the CPU with the reason for interrupting being burst termination. By tampering with the interrupt service routine's return stack the CPU breaks out of the infinite loop.

## 2.3.4 Interrupt Control 0 0 1 1

The field is 0. This opcode is a special "no op" command. When protocol commands are passed by interrupting the IOP it sets PACK = 1 and enters an "interrupted" state for the duration of the command execution. The I/O processor will remain in this state (with normal operations suspended) until the CPU declares the command's operation to be complete by strobing the I/O processor's INT bit. For burst operation, the global interrupt disable feature can't be used because the active I/O processor must be able to interrupt the CPU to terminate the burst. Before a burst operation, all resident I/O processors are sent this "no op" and are put into the "interrupted" state by the command handshaking. The interrupt bit of the I/O processor to be used for burst is strobed and that I/O processor "revives" to perform the burst. After the burst, all I/O processors with PACK = 1 are strobed, reviving them (by allowing completion of the "no op" command) to continue with their normal operations.

## 2.3.5 Interface Control 0 1 0 0

The field, from 0 to 9, selects one of the 10 interface control operations. These are immediate execution with no data involved (except a parallel poll response byte which is placed in the input buffer after that operation).

Table 2-2. Interface Control Fields

| Field | Command                      |

|-------|------------------------------|

| 0     | ABORT I/O.                   |

| 1     | Set REN = 1.                 |

| 2     | Set REN = 0.                 |

| 3     | Set ATN = 0.                 |

| 4     | Perform Parallel Poll.       |

| 5     | Send "MY TALK ADDRESS."      |

| 6     | Send "MY LISTEN ADDRESS."    |

| 7     | Send EOL character sequence. |

| 8     | BREAK I/O.                   |

| 9     | RESUME I/O.                  |

## 2.3.6 Read Auxiliary 0 1 1 1

This is a diagnostic not used by the I/O ROM.

## 2.3.7 Write Control 1 0 0

The field is a five-bit register number. This opcode causes the IOP to wait for data bytes which are to be written into consecutive control registers beginning with the one indicated in the field. The CPU sets the CED bit equal to 1 with the last byte sent. This opcode implements the CONTROL statement. However, there are five control registers (R25 through R29) that the I/O ROM hides from BASIC programmers. These registers are:

R25 - (least significant byte) character count

R26 - (most significant byte) character count

These two bytes contain a 16-bit binary integer which the I/O processor uses to terminate a data transfer by character count.

R27 - Input termination character

This byte is used by the I/O processor as a termination match character when bit 2 is set on an input interrupt command.

R28 - ASSERT byte

The ASSERT operation is performed by writing the byte to be asserted into this control register.

R29 - Service Request Byte

This is the byte that is to be sent to the HP-IB bus if this processor is serially polled.

### 2.3.8 Output 1 0 1 0

The field is:

| MSB | 0 | 0 | INTR<br>SIMPLE | 0 | LSB |

|-----|---|---|----------------|---|-----|

|     | 3 | 2 | 1              | 0 |     |

This opcode commands a simple (bit 1 = 0) or interrupt (bit 1 = 1) output operation. The I/O processor either waits for data bytes to output (simple) or interrupts the CPU with the reason for interrupting being readiness to transmit one or more bytes. In both cases the operation is terminated by the CPU setting CED = 1 in the calculator control register just before the last byte is put into the output buffer.

### 2.3.9 Send Commands 1 0 1 1

The field is 0. The send commands tell the processor the next bytes should be in command mode as opposed to data mode. This is an HP-IB opcode and causes that interface to handshake the data bytes over the HP-IB bus with ATN = 1 (true).

### 2.3.10 Write Auxiliary 1 1 1 0

Like read auxiliary, this opcode is a diagnostic not used by the I/O ROM.

## 2.4 What Happens When the I/O Processor Interrupts the CPU?

When an I/O processor interrupts the CPU, the first thing the CPU service routine does after identifying the processor is to read the input buffer to let the processor know that the service request is now being handled. The processor then places a byte into the input buffer to tell the CPU why it was interrupted. The recognized values of this byte are:

Table 2-3. IOP Interrupt Byte

| Byte            | Interrupt Reason                |

|-----------------|---------------------------------|

| 0 0 0 0 0 0 0 0 | Interrupt output.               |

| 0 0 0 0 0 0 0 1 | Burst termination.              |

| 0 0 0 0 0 0 1 0 | ON INTR condition met.          |

| 0 0 0 0 0 0 1 1 | Self-test passed.               |

| 0 0 0 0 0 1 0 0 | Interrupt input.                |

| 0 0 0 0 0 1 1 0 | Finished EOL sequence.          |

| 1 1 1 1 1 0 1 1 | Self-test failed.               |

| 1 1 1 1 1 1 1 1 | Invalid I/O operation.          |

| 0 X X X X X 1 1 | Interface type dependent error. |

**Interrupt Output:** The IOP is prepared to process one or more output data bytes (during an output transfer by interrupt) and is interrupting to get some data from the CPU.

**Burst Termination:** The IOP has determined that the current burst operation is finished and the CPU should abandon its infinite loop.

**ON INTR Condition Met:** Some interrupt condition masked in control register 1 (interrupt mask) has occurred.

**Self-Test Passed:** The IOP has completed its reset procedure and passed the self-test.

**Interrupt Input:** Like interrupt output with the IOP indicating it has bytes for the CPU.

**Finished EOL Sequence:** The IOP has completed sending the EOL character sequence after an interrupt output.

**Self-Test Failed:** The IOP has completed its reset procedure and has failed the self-test.

Invalid I/O Operation: The IOP cannot execute the protocol commands it has received (for example, a serial interface was sent a parallel poll command).

Interface-Type Dependent Error: The IOP is reporting an interface dependent error. These errors are documented in the I/O ROM manual. Adding 112 (decimal) to bits 6 through 2 in the interrupt byte will give you the error number.

Following is an interpretation of the "reason byte."

Reason byte: X X X X X X 1 1 - "Reports"

These are error reports or the "self-test passed" report. The I/O ROM displays a message for the errors. You need not do anything as far as the IOP is concerned.

Reason byte: 0 0 0 0 0 1 1 0 - "Finished EOL sequence"

0 0 0 0 0 1 0 - "ON INTR trigger"

These two are also reports in the sense that the IOP is telling the CPU it is finished sending the preprogrammed end-of-line character sequence in the first case and one of the register 1 interrupt mask conditions has been met in the second case. The I/O ROM records an EOL branch indicator for the appropriate ON EOT or ON INTR. You need not do anything.

The above reasons for interrupting don't really obligate you, as the I/O programmer, to do anything besides acknowledge the interrupt in your service routine. Burst termination, interrupt input, and interrupt output do require you to take appropriate action.

Reason byte: 0 0 0 0 0 0 1 - "Burst termination"

You must break the CPU out of its infinite loop. Refer to Burst I/O.

Reason byte: 0 0 0 0 0 0 0 - "Interrupt output"

0 0 0 0 1 0 0 - "Interrupt input"

See figures 2-5 and 2-6 at the beginning of this section for details of these reason bytes.

---

PERFORMING I/O OPERATIONS

---

### 3.1 Introduction

This section defines and illustrates the operation high-level I/O. It is divided into three parts: flowcharts which illustrate the operation of high-level and utility routines, utilities and sample code, and the description of the steps involved in performing an I/O operation.

### 3.2 I/O Operation Flowcharts

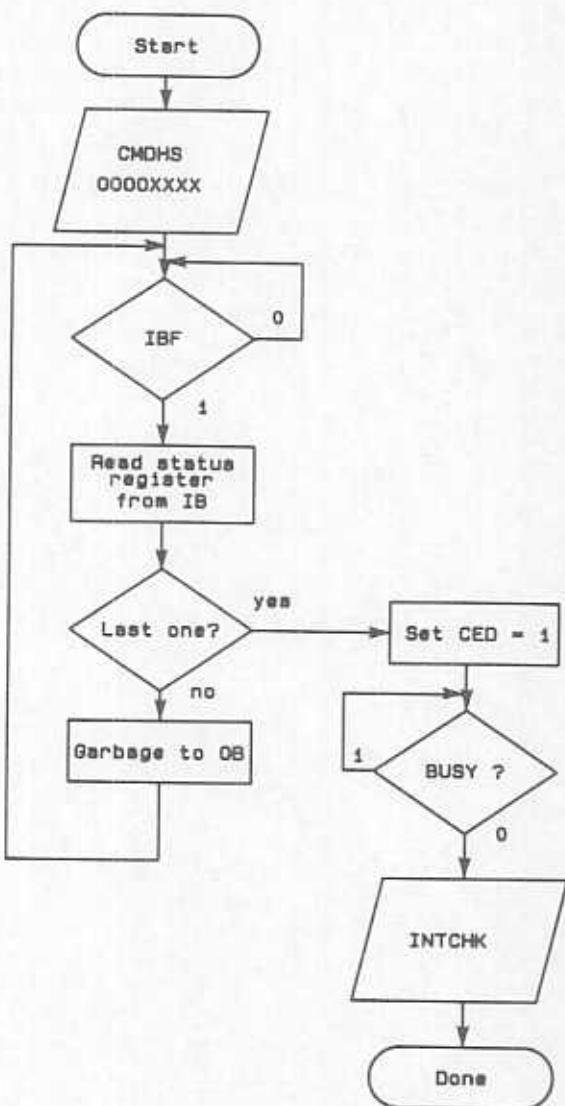

The flowcharts shown assume that the reset and interrupt facilities are set up.

Figure 3-1. Read Status

Figure 3-2. Simple Input

### Section 3: Performing I/O Operations

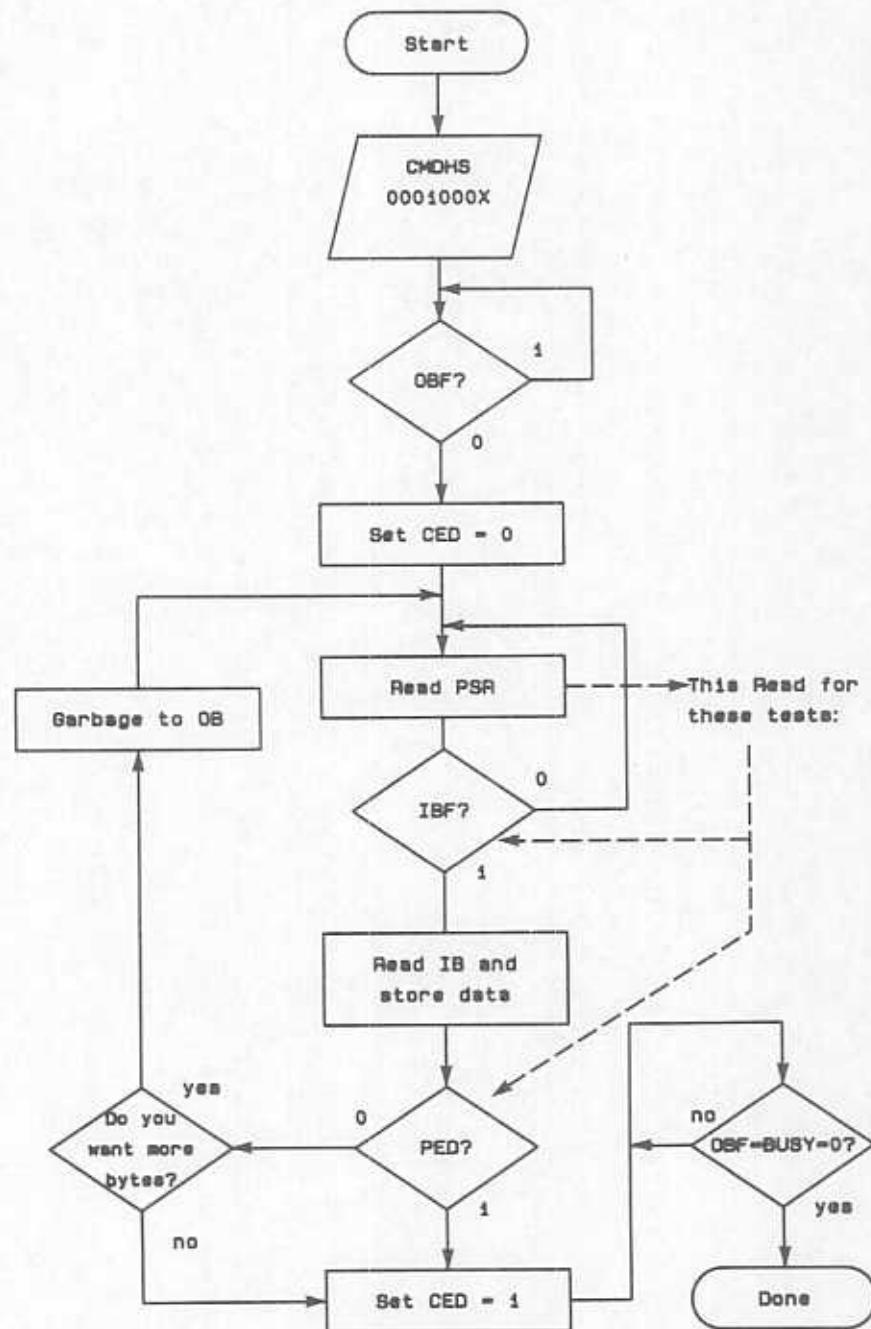

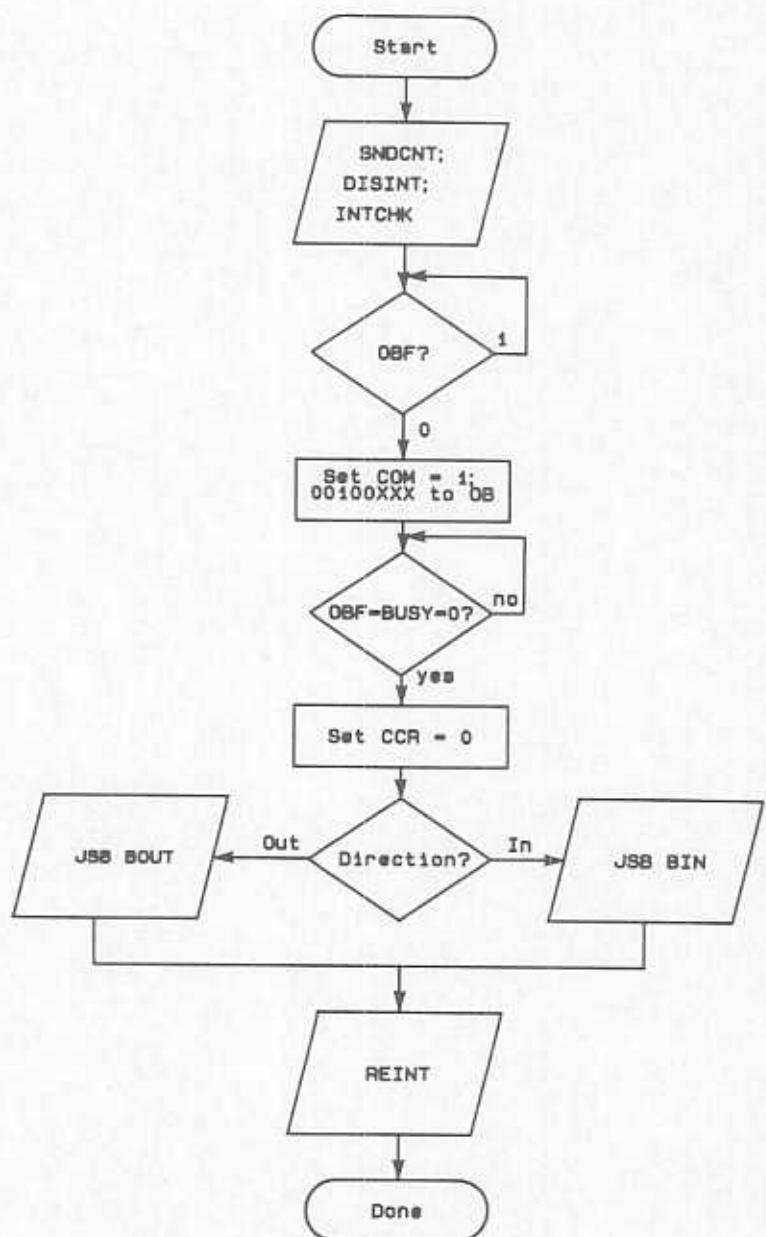

Figure 3-3. Burst I/O

Figure 3-4. Burst Loops

Figure 3-5. Disable All Interrupts

Figure 3-6. Re-enable All Interrupts

Figure 3-7. Write Control

Figure 3-8. Initiate Interrupt Input

Figure 3-9. Initiate Interrupt Output

Figure 3-10. Send Byte Count

Figure 3-11. Simple Output

### 3.3 I/O Operations: Utilities and Sample Code

#### 3.3.1 Register Conventions

In the examples of binary code throughout this manual, it is assumed that all data transfers take place between the IOP and the CPU registers. Therefore, the choice of registers, data sources, and sinks is up to you.

The sample code is written for a binary program. If you are going to write ROM-based code, refer to the Assembler ROM manual for a discussion of the changes you should make to convert from the binary program format. To make things easier to understand, a few register conventions are adopted here:

R22,23      Base address (BINTAB or stolen RAM pointer, if you are writing ROM code).

##### I/O Addresses:

R24,25      Pointer to the IOP calculator control register/ processor status register port.

R26,27      Pointer to the IOP output buffer/input buffer port.

##### For String Enter or Output:

R30,31      String length.

R32,33      String pointer.

##### Other:

R35      Command byte for SEND CMD operations (send a bus protocol command, that is, unlisten).

R36      Command byte for I/O protocol commands.

R37      Scratch for flag tests, etc.

#### 3.3.2 Interrupting Versus Noninterrupting IOP Commands

In general, the IOPs should be dealt with in discrete, mutually exclusive operations. One exception to this is when doing interrupt I/O with a full duplex interface or with two or more different interfaces. There are some protocol commands that must be able to operate at once, even if the interface is busy at the time.

They are passed to the IOP by a handshake method which interrupts the IOP from whatever it is currently doing. Because they are either noninterfering (read, status) or benevolently interfering (abort, resume), these interrupting commands are given the privilege of bypassing the normal wait when the IOP is busy.

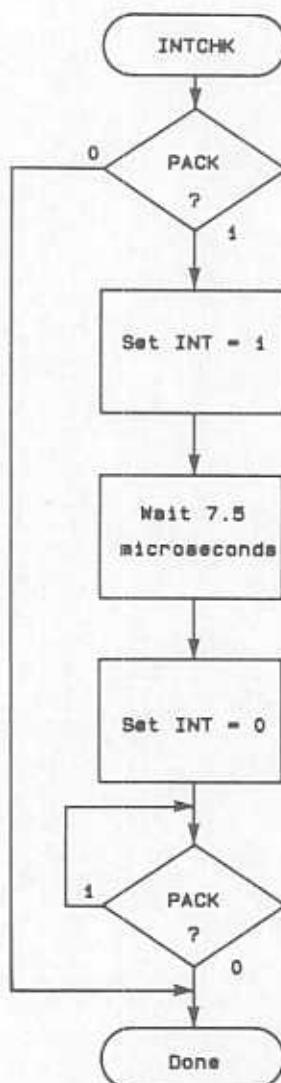

The best way to handle the different command passing procedures is to simply have two command handshaking routines (one for the interrupting commands and another for direct commands), and two operation termination routines (refer to the DIRCMD, INTCMD, INTCHK, and O=B=0 utilities). If you are doing interrupt I/O with a full duplex interface, the interrupting commands will allow you to do those operations that will work. In all other cases, the difference between the two types of commands is one of handshaking method, because the CPU is presumably only doing one thing at a time.

We will discuss the I/O operations as individual events with a beginning, a middle, and an end. The handshaking difference shows up in the beginning of an operation as the method of passing the command, and also at the end as the method used to terminate the operation. (Wait until the IOP has finished the operation in the case of direct commands and make sure that the IOP is "uninterrupted" and returned to its presumably interrupted task in the case of the interrupt-type commands). In the following discussions, it is assumed that all operations are discrete (interrupt I/O is discussed separately) and the only task interrupted by an interrupt-type command is the task of idling while waiting for a command.

#### 3.4 Definition of an I/O Operation

An operation is one complete interaction with an IOP. For instance, an input operation includes the configuration and addressing (if needed) as well as the transfer of data. A protocol command is an order to an IOP to execute some part of an operation. A typical data transfer operation will involve a number of protocol commands.

An interrupt-type protocol command involves three stages of execution:

1. The IOP is interrupted by the CPU.

2. The command is given and executed by the IOP (using the CPU if necessary).

3. The IOP then returns to its previous task.

The utility routine INTCMD will interrupt the IOP and pass the protocol command to it. The utility routine INTCHK will uninterrupt the IOP. A direct command is passed to the IOP by the utility routine DIRCMD. This routine will wait until the IOP is not busy and then handshake the command. The IOP does not need to be uninterrupted after a direct command but it is common to wait until the IOP returns to idle after the command by calling the utility routine O-B-0.

For purposes of discussion the operations will be grouped into these categories:

- Status and Control.

- Simple Input/Output.

- Primary Addressing and HP-IB Interface Message.

- Miscellaneous Utilities.

- Burst Input/Output.

- Interrupt Operations.

For a discussion of the protocol commands as an instruction set and explanation of bits, ports, and addresses refer to section 2.

#### 3.4.1 Command Handshaking Utility Subroutines

There are a few common waits and handshakes involved in many I/O operations and they are presented here as subroutines which you can include in the binary code you write. These are examples that make the code that follows easier to understand.

These utilities follow the register conventions outlined at the beginning of this section.

Wait until the input buffer is full:

```

IBF=1    LDBD R37,R24      !READ THE PSR

JEV IBF=1      !JIF IBF = 0

RTN

```

Wait until the output buffer is empty:

```

OBF=0    LDBD R37,R24      !READ THE PSR

JNG OBF=0      !JIF OBF = 1

RTN

```

### Section 3: Performing I/O Operations

Send the command byte in R36 to the IOP by direct method:

```

DIRCMD JSB X22,0=B=0      !WAIT FOR OBF=BUSY=0

LDB R37,=2      !SET CMD BIT TO 1

STBD R37,R24    ! IN CCR

STBD R36,R26    !SEND THE COMMAND BYTE TO OB

JSB X22,OBF=0    !WAIT TILL THE IOP HAS IT

CLB R37      !CLEAR THE CMD BIT

STBD R37, R24   ! IN CCR

RTN

```

Wait until the output buffer is empty and the IOP is not busy. This will terminate direct command operations.

```

O=B=0  LDBD R37,R24      !READ THE PSR

ANM R37,=202      !MASK OFF OBF AND BUSY

JNZ O=B=0      !JIF THEY'RE NOT BOTH 0

RTN

```

Send the command in R36 to the IOP by interrupting it:

```

INTCMD STBD R37,=GINTDS  !DISABLE ALL INTERRUPTS

LDB R37,=1      !SET THE INT BIT TO 1

STBD R37,R24    ! IN THE CCR

INTCM1 LDBD R37,R24      !WAIT UNTIL THE IOP SEES IT

ANM R37,=10      ! AND ACKNOWLEDGES

JZR INTCM1      ! (JIF PACK = 0)

STBD R37,=GINTEN !OTHER INTERRUPTS OK NOW

STBD R36,R26    !STUFF THE COMMAND INTO OB

LDBD R37,R26    !BE SURE THE IB IS EMPTY

LDB R37,=2      !SET CMD BIT & CLEAR INT BIT

STBD R37,R24    ! IN THE CCR TO START IOP

JSB X22,OBF=0    !WAIT TILL IOP GETS COMMAND

CLB R37      !CLEAR THE CMD BIT

STBD R37,R24    ! IN THE CCR

RTN

```

### Section 3: Performing I/O Operations

Check to see if the IOP is busy. If it is, the interrupt bit (INT in the CCR) must be strobed. The test for PACK=1 allows this routine to be called for an IOP which wasn't interrupted in the first place. Use this code to terminate interrupt-type command operations:

```

INTCHK  LDBD R37,R24      !READ THE PSR

ANM  R37,=10      !MASK OFF THE PACK BIT

JNZ  INTCH1      !IF PACK = 1

INTRTN  RTN               !ELSE, IT'S DONE ALREADY

INTCH1  LDB  R37,=1       !STROBE THE INT BIT

STBD R37,R24     ! IN THE CCR

JSB   X22, INTRTN ! (waste some time)

CLB   R37       ! RESET THE BIT TO 0

STBD R37,R24

INTCH2  LDBD R37,R24      !NOW WAIT UNTIL PACK = 0

ANM  R37,=10

JNZ  INTCH2

RTN

```

### Section 3: Performing I/O Operations

Send the byte in register R35 as a bus command (that is, the equivalent to SEND <s.c.>; CMD <R35>):

```

SNDCMD LDB R36,=260      !PROTOCOL COMMAND FOR SEND

JSB X22,DIRCMD           ! GOES TO THE IOP

LDB R37,=4                !ONLY ONE BYTE, SO SET CED

STBD R37,R24              ! IN THE CCR

STBD R35,R26              !THE BYTE (DIRCMD DID OBF=0)

JSB X22,O=B=0             ! WAIT UNTIL THE IOP IS DONE

RTN

```

#### 3.4.2 Status and Control Operations

These operations correspond to the STATUS and CONTROL keywords in the I/O ROM and are implemented in assembler code through the I/O protocol commands "Read Status" (opcode = 0000) and "Write Control" (opcode = 1000 or 1001). There are some control registers available to the assembly language I/O programmer which are not directly accessible through the I/O ROM. They will be discussed separately at the end of this section.

The status operation is an interrupt-type command because it might be needed while an interface is busy with an interrupt input or output transfer. Control operations are considered direct commands because they should not be executed while a transfer is in progress. (They change the configuration of the interface.)

Table 3-1. Execution Times (milliseconds)

|           | HP-IB    | Serial   | BCD      | GP-IO     |

|-----------|----------|----------|----------|-----------|

| Assembler | 0.9/0.15 | 0.85/0.3 | 0.7/0.18 | 0.65/0.15 |

| BASIC     | 9/3      | 11/3     | 9/3      | 9/3       |

These times are given as:

$$\frac{\text{<time to do one byte's worth>}}{\text{<time for each extra byte>}}$$

### 3.4.3 Status and Control Utility Subroutines

These examples assume that the CPU registers are already set up as shown under Register Conventions. The string length in register pair R30,31 is the number of bytes to be read in the status operation and written in the control operation. In addition, the starting status and control register number is in CPU register R34 and is assumed to be valid.

|        |                 |                                |

|--------|-----------------|--------------------------------|

| STATUS | LDB R36,=0      | !Status opcode = 0             |

|        | ORB R36,R34     | !Starting register is field    |

|        | JSB X22, INTCMD | !Tell the IOP to do status     |

| STAT10 | JSB X22,IBF=1   | !Wait till IOP gets a byte     |

|        | LDBD R37,R26    | !Read the status byte          |

|        | PUBD R37,+R32   | !Store it                      |

|        | DCM R30         | !Was that the last one?        |

|        | JZR STAT20      | ! (JIF yes - last one)         |

|        | STBD R#,R26     | ! else ask for another one     |

|        | JMP STAT10      | ! and go get it                |

| STAT20 | LDB R37,=4      | !We're done so set CED         |

|        | STBD R37,R24    | ! in the CCR                   |

|        | JSB X22,0=B=0   | !Wait for IOP to finish up     |

|        | JSB X22,INTCHK  | !Uninterrupt the IOP           |

|        | RTN             |                                |

| CTRL   | LDB R36,=200    | !Control (opcode = 100)        |

|        | ORB R36,R34     | ! field = starting reg. #      |

|        | JSB X22,DIRCMD  | !Tell IOP to do control write  |

| CONT10 | JSB X22,OBF=0   | !Wait till IOP is ready for    |

|        | POBD R36,+R32   | ! this next byte.              |

|        | DCM R30         | !Is this the last one?         |

|        | JZR CONT20      | ! (JIF yes - last one)         |

|        | STBD R36,R26    | ! otherwise just send the byte |

|        | JMP CONT10      | ! and go for the next one      |

| CONT20 | LDB R37,=4      | !On last one set CED           |

|        | STBD R37,R24    | ! in the CCR                   |

|        | STBD R36,R26    | ! and then send the byte.      |

|        | JSB X22,0=B=0   | !Wait till the IOP is done     |

|        | RTN             |                                |

The control and status operations differ in various interfaces only in the registers which are implemented by a particular interface. Legal operations correspond to those that are legal to use with the I/O ROM statements: STATUS and CONTROL.

#### 3.4.4 Special Control Operations Not Available With BASIC

There are five control registers in each interface which are not visible to the BASIC programmer. These are control registers 25 through 29. The five registers implement the following four functions:

1. Transfer Count. Before each burst transfer or interrupt input transfer, the IOP must receive a byte count. This is the count that terminates a burst transfer and, among other possible conditions, an interrupt input transfer. This count is specified by writing it to control registers 25 (least significant byte) and 26 (most significant byte).

2. Delimiter Character. Interrupt input transfers can also be terminated by the receipt of a particular byte value. This value is specified by writing it to control register 27. This corresponds to the keyword "DELIM" in the I/O ROM.

3. Assert Byte. The ASSERT operation is performed by writing the byte to be asserted to control register 28. The difference between this operation and a write to control register 2 (they both put the byte into control register 2) is that ASSERT is implemented as an interrupt-type command. Thus, the operation can take place even while the interface is busy.

4. Service Request. The REQUEST operation is performed by writing the response byte to control register 29. This sets up a service request on the HP-IB interface, sends a break over the serial interface and is an error for the BCD and GPIO interfaces.

These special control write operations are distinguished from the normal control write operations by the command handshaking method used. For the Assert and Request operations the handshaking is always interrupt-type. For the writing of byte count and input termination match byte, the handshaking is interrupt-type if the interface is full duplex (FDPX bit in PSR is equal to 1). Otherwise the handshaking is direct-type. These control registers can be accessed using the sample CONTROL code above by making the following two substitutions when interrupt-type handshake is needed: replace DIRCMD with INTCMD and replace O=B=0 with INTCHK. Because the byte counts are known, the simplified versions are presented below. The assert, response, or termination byte is assumed to be in R34. The count is assumed to be in register pair R34,35.

Send byte count to a full duplex interface:

```

ICOUNT      LDB  R36,=231      !Protocol = write control 25

JSB  X22,INTCMD    !(full duplex)

STBD R34,R26      !Send least significant byte

JSB  X22,OBF=0      !Wait till IOP gets first one

LDB  R37,=4        !This is last, so set CED

STBD R37,R24      ! in the CCR

STBD R35,R26      !Send most significant byte

JSB  X22, INTCHK   !Wait till IOP is done

RTN

```

Send count to a nonfull duplex interface:

```

DCOUNT      LDB  R36,=231      !Protocol = write control 25

JSB  X22,DIRCMD    !(NOT full duplex)

STBD R34,R26      ! first byte (DIRCMD did OBF)

JSB  X22,OBF=0      !Wait for IOP to get first

LDB  R37,=4        !Second is last so set CED

STBD R37,R24      ! in the CCR

STBD R35,R26      !Second (most significant)

JSB  X22,O=B=0      !Wait till IOP is done

RTN

```

Send delimiter character to a full duplex interface:

```

ITERM      LDB  R36,=233      !Protocol = write control 27

JSB  X22,INTCMD    !(full duplex)

LDB  R37,=4        !First is last, so set CED

STBD R37,R24      ! in the CCR

STBD R34,R26      !Send the byte

JSB  X22,INTCHK   !Uninterrupt the IOP

RTN

```

Send delimiter character to a nonfull duplex interface:

```

DTERM      LDB  R36,=233      !Protocol = write control 27

JSB  X22, DIRCMD   !(NOT full duplex)

LDBD R37,=4        !First is last, so set CED

STBD R37,R4        ! in the CCR

STBD R34,R26      !Send the byte

JSB  X22,O=B=0      !Wait till IOP is done

RTN

```

Note that the count and termination character can be specified in one operation by sending the three bytes in order.

Assert the byte in R34 (any kind of interface):

```

ASSERT      LDB  R36,=234      !Protocol = write control 28

JSB  X22,INTCMD    !This is ALWAYS interrupting

LDB  R37,=4       !Only one byte so set CED

STBD R37,R24      ! in the CCR

STBD R34,R26      !Send the assert byte

JSB  X22,INTCHK    !Wait till IOP is done

RTN

```

Request service or break:

```

RQUEST      LDB  R36,=235      !Protocol = write command 29

JSB  X22,INTCMD    !This is ALWAYS interrupting

LDB  R37,=4       !Only one byte so set CED

STBD R37,R24      ! in the CCR

STBD R34,R26      !Send the response byte

JSB  X22,INTCHK    !Wait till IOP is done

RTN

```

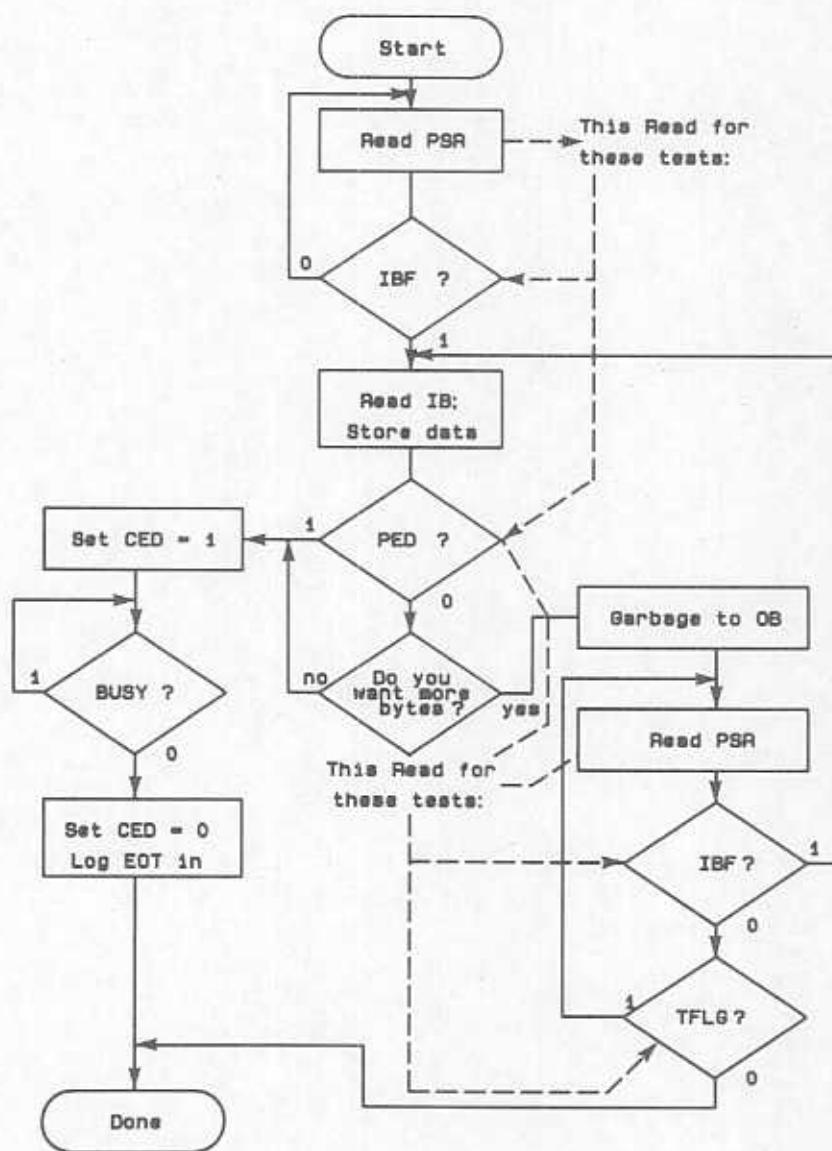

### 3.4.5 Simple Input/Output

These operations perform programmed I/O where the handshaking of transferred data is handled directly by the CPU in the normal execution flow of its binary program. They correspond to but need not be limited to the I/O ROM keywords ENTER and OUTPUT. Multiple concurrent I/O transfers can be performed with these simple operations so long as no interface needs to operate in a full duplex mode. A binary program which manages enough of an interrupt service routine to reset the interfaces at power-on could run four concurrent I/O operations on four interfaces. By polling the input interfaces for input buffer full and the output interfaces for output buffer empty, the CPU can control the data transfers entirely.

The operations described here assume that the interface involved has been configured and addressed as needed (send bus command operations are discussed later). It is assumed that the number of bytes to be transferred is indicated by the string length in R30,31 and the data source or sink is pointed to by the contents of R32,33. Where data comes from and where it goes is, of course, up to the I/O programmer. The transfers to and from all interfaces always involve one or more bytes.

The BASIC language I/O programmer has a large variety of data types and structures that can be specified in ENTER and OUTPUT statements. The keyword code in the I/O ROM translates these data types and structures into a string of bytes before it outputs them to an interface (using identical translation procedure regardless of interface type). They are translated into a string of bytes after they are input for an ENTER operation (again the interface type makes no difference). When coding I/O operations directly in assembly language you must manage your own data formats. The content of the byte or bytes transferred depends upon your application and the type of interface.

In general, the HP-IB interface isn't affected by the content of a given data byte; neither is the serial interface (except for some control codes). The BCD interface requires a restricted set of ASCII symbols in a particular format depending on the configuration of the ports. The GPIO expects only to handle even numbers if you are using one of the 16-bit ports.

#### Output

For outputs, an interface must be configured (refer to Control), addressed (refer to Send), given the output protocol command, and given a byte or a series of bytes to output with the CED (calculator end data) bit in the CCR set to 1 just before transfer of the last byte. The interface will send its end-of-line character sequence (as specified in control registers 16 through 23) and then go into its nonbusy state (recall that the BCD interface does not have an end-of-line character sequence).

The configuration and addressing need not be repeated before each output operation if you know that it has already been done. The output protocol command must be used before a data byte is output to an interface if the CED bit was set for the previous data byte output to the same interface. You may omit the setting of the CED bit and the sending of the next output protocol command if you keep track of whether or not the interface is busy (the I/O ROM does this to allow the OUTPUT USING # option).

#### Input

Inputs are similar to outputs in configuration, addressing, and command sequence. There are some added complications involved in the termination of the transfer. The CPU may terminate an input at any time by setting the CED bit in the CCR, similar to the OUTPUT termination.

The IOP may also decide to terminate an input operation by setting the PED (processor end data) in the PSR. Whether or not this occurs depends upon the particular interface and the option bits included in the input protocol command. The three option bits are: bit 3 (count), bit 2 (character), and bit 0 (EOI). Bits 7 through 4 are the command opcode (0001). Bit 1 specifies whether the input is a simple input (bit 1 = 0) or an interrupt input (bit 1 = 1). We will examine these options for each interface.

### HP-IB Input

The HP-IB interface allows you to use any of the three options. If you specify termination by count, you must provide the count (by writing to control registers 25 and 26) before beginning the input operation. The same holds true for the character termination option (you must provide the termination match character by writing it into control register 27). The EOI condition on the HP-IB interface is taken to be the receipt of a data byte (device dependent message) with the END message (EOI) true.

### Serial Input

The serial interface also allows you to use any of the three options, but this interface will use the EOI condition whether or not you specify it! For this interface, the EOI condition is an incoming character that matches one of the termination characters specified in the control registers 12, 13, 14, or 15 along with the enabling bits in control register 11. Note that these four termination match characters are in addition to the one that you may or may not have specified as the termination character in special control register 27.

### BCD Input

The BCD interface does not use or allow any of these input termination operations. The BCD interface will only accept the protocol command 21 (octal) as the simple input command.

### GPIO Input

The GPIO interface allows the count and character termination options and completely ignores the EOI bit. If you are operating in 16-bit mode, the count termination option may be used but the character termination option may not be used.

Besides these specified input termination conditions, the BCD interface will set the PED bit when it has exhausted the bytes needed to transfer the data defined by its current primary address and port configuration. The other interfaces will just keep on sending bytes until the CED bit is set, or one of the enabled and allowed conditions is met.

It is the responsibility of the CPU to recognize the assertion of the PED bit, set CED in response, and send a new input protocol command before asking for additional input bytes.

### Execution Speeds for Simple Enter and Output

Execution speeds for simple enter and output operations depend upon external events as well as I/O protocol execution so they will be discussed rather than simply listed. The BASIC execution times for equivalent operations depend heavily on formatting options and will be mentioned but not discussed in detail.

#### HP-IB Interface

The HP-IB interface requires 0.3 milliseconds to process an input protocol command and 0.25 milliseconds to output each data byte (device dependent message). It will process an output protocol command in 0.4 milliseconds and send each data byte in 0.16 milliseconds. This means that about 4,000 bytes per second can be input and about 6,000 bytes per second can be output. These times assume that any devices on the HP-IB interface bus are fast enough to keep up with the interface at these speeds.

#### Serial Interface

The serial interface requires about 0.5 milliseconds to process either an input or output protocol command. Due to the timing methodology used and the interface, the execution time for the protocol command is lost in the baud rate, FIFO (first in, first out) operations, and external device response. Because 9600 baud is the maximum data transfer rate available on the serial interface, this will limit the speeds at which bytes can be transferred to about 960 bytes per second (assuming 10 bits per character). The CPU has no trouble keeping up with this speed. If you are operating under conditions that guarantee you will be inputting bytes that are already in the FIFO buffer then you can expect to get them out in approximately 0.3 milliseconds each.

#### BCD Interface

The BCD interface requires 0.3 milliseconds to process an input protocol command and 0.25 milliseconds for each byte actually input. The time for the output protocol command is 0.6 milliseconds and 0.25 milliseconds per data byte. Remember that each data byte corresponds to one port digit (in the BCD interface) and that the number of bytes transferred depends upon signs, exponents, and punctuation, as well as the number of port digits involved. The BCD interface will always include a line feed character at the end of each reading where it sets the PED bit.

If we assume that the externally connected device is as fast as the interface, then we can get some "transfers per second" figures. If we just use one digit, we can output one data byte but must input two data bytes (digit and line feed; recall that there is a sign character if you're using the mantissa instead of the function digit as assumed here) so we can expect to get about 1,100 transfers out per second and about 1,200 transfers in per second.

If we look at a large format number with eight mantissa digits and an exponent (which is always three digits as far as the BCD interface is concerned) then we need to output 14 digits and input 15 digits. The result will be about 250 transfers per second in either direction.

#### GPIO Interface

The protocol command handshake and the transfer of a 16-bit number (two data bytes) takes one millisecond in either direction using the GPIO interface. For eight-bit format transfers, the command handshaking takes 0.4 milliseconds and each data byte transferred also takes 0.4 milliseconds in either direction. This translates into 1000 transfers per second for 16-bit data and 2500 transfers per second for eight-bit data.

#### BASIC

The comparable times in BASIC depend upon the overhead required for the IMAGE specifiers. In general, there will be approximately 20 milliseconds for the interpreter and statement set-up. There will also be at least 50 microseconds per character transferred depending upon what kind of transformations are being done to the data. While you can escape this overhead by doing your I/O operations directly from assembler code, you must do something in the way of sourcing and/or sinking data. This will take some time in addition to the time for the CPU-IOP transfer.

### 3.4.6 Simple Input and Simple Output Utility Subroutines

The examples below assume the correct number of bytes to be transferred is in register pair R30,31 and the source/sink pointer is in register pair R32,33. For input, it is assumed that a valid bit mask for the termination options is available in register R34. It is also assumed that the interface involved has already been addressed as needed and pointers to its CCR/PSR and OB/IB are in register pairs R24,25 and R26,27.

|         |                |                              |

|---------|----------------|------------------------------|

| INPUT   | LDB R36,=20    | !Protocol = simple input     |

|         | ORB R36,R34    | ! or in the options          |

|         | JSB X22,DIRCMD | !Tell IOP to do input        |

| INloop  | JSB X22,IBF=1  | !Wait till there's a byte    |