# Series 9800 Desktop Computers

## HP 98036A Installation and Service

#### Warranty Statement

Hewlett-Packard products are warranted against defects in materials and workmanship. For Hewlett-Packard Desktop Computer Division products sold in the U.S.A. and Canada, this warranty applies for ninety (90) days from date of delivery.\* Hewlett-Packard will, at its option, repair or replace equipment which proves to be defective during the warranty period. This warranty includes labor, parts, and surface travel costs, if any. Equipment returned to Hewlett-Packard for repair must be shipped freight prepaid. Repairs necessitated by misuse of the equipment, or by hardware, software, or interfacing not provided by Hewlett-Packard are not covered by this warranty.

NO OTHER WARRANTY IS EXPRESSED OR IMPLIED, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. HEWLETT-PACKARD SHALL NOT BE LIABLE FOR CONSEQUENTIAL DAMAGES.

\*For other countries, contact your local Sales and Service Office to determine warranty terms.

# HP 98036A

## Serial I/O Interface

### Installation and Service Manual

Hewlett-Packard Desktop Computer Division

3404 East Harmony Road, Fort Collins, Colorado 80525

Copyright by Hewlett-Packard Company 1979, 1981

## Printing History

New editions of this manual will incorporate all material updated since the previous edition. Update packages may be issued between editions and contain replacement and additional pages to be merged into the manual by the user. Each updated page will be indicated by a revision date at the bottom of the page. A vertical bar in the margin indicates the changes on each page. Note that pages which are rearranged due to changes on a previous page are not considered revised.

The manual printing date and part number indicate its current edition. The printing date changes when a new edition is printed. (Minor corrections and updates which are incorporated at reprint do not cause the date to change.) The manual part number changes when extensive technical changes are incorporated.

December 1979...First Edition

January 1981...Second Edition (adds Option 002).

### NOTICE

---

The information contained in this document is subject to change without notice.

HEWLETT-PACKARD MAKES NO WARRANTY OF ANY KIND WITH REGARD TO THIS MATERIAL, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. Hewlett-Packard shall not be liable for errors contained herein or for incidental or consequential damages in connection with the furnishing, performance or use of this material.

This document contains proprietary information which is protected by copyright. All rights are reserved. No part of this document may be photocopied, reproduced or translated to another program language without the prior written consent of Hewlett-Packard Company.

# Table of Contents

## Chapter 1: General Information

|                     |   |

|---------------------|---|

| Manual Introduction | 1 |

| Chapter Summaries   | 1 |

| 98036A Description  | 2 |

| Specifications      | 2 |

| Cable Options       | 3 |

## Chapter 2: Installation

|                                          |    |

|------------------------------------------|----|

| Introduction                             | 7  |

| Hardware Configuration (Exterior Access) | 7  |

| Bit Rate (or Baud) Switch                | 7  |

| Select Code Switch                       | 8  |

| Hardware Configuration (Interior Access) | 8  |

| Interface Disassembly                    | 10 |

| Setting the Switches                     | 12 |

| Mode Word Switches                       | 12 |

| Input/Output Mode Switch                 | 14 |

| RS-232C Driver Switch                    | 15 |

| Internal/External Clock Switch           | 15 |

| Clear to Send Switch                     | 15 |

| Interface Installation                   | 16 |

## Chapter 3: The Interface Registers

|                                   |    |

|-----------------------------------|----|

| Introduction                      | 17 |

| Bit Position Values               | 17 |

| R4 Registers                      | 18 |

| Transmit Data Register (R4A)      | 18 |

| Received Data Register (R4B)      | 18 |

| The USART Mode Word (R4C)         | 19 |

| The USART Control Word (R4D)      | 20 |

| The USART Status Word (R4E)       | 21 |

| R5 Registers                      | 22 |

| R5OUT Register                    | 22 |

| R5IN Register                     | 23 |

| R6 Registers                      | 24 |

| R6OUT Register (Standard Cable)   | 24 |

| R6IN Register (Standard Cable)    | 25 |

| R6OUT Register (Option 001 Cable) | 26 |

| R6IN Register (Option 001 Cable)  | 27 |

## Chapter 4: Talking to the Interface

|                              |    |

|------------------------------|----|

| Introduction                 | 29 |

| Setting Control or Data Mode | 29 |

| Status                       | 30 |

| Interface Status             | 30 |

| USART Status                 | 31 |

|                                              |       |

|----------------------------------------------|-------|

| Resets .....                                 | 32    |

| Programmed Interface Reset .....             | 32    |

| Error Bit Reset .....                        | 33    |

| USART Reset .....                            | 33    |

| USART Mode Word .....                        | 34    |

| Transmitter/Receiver Control .....           | 36    |

| Break and R4 Modem Control Signals .....     | 37    |

| Sending a "break" .....                      | 37    |

| Clear to Send/Request to Send .....          | 38    |

| Data Set Ready/Data Terminal Ready .....     | 38    |

| Additional Modem Signals .....               | 39    |

| Carrier Detect .....                         | 40    |

| Other Modem Signals .....                    | 41    |

| Half/Full Speed Interface Control .....      | 41    |

| Interrupts .....                             | 41    |

| Enabling Transmitter Interrupts .....        | 42    |

| Enabling Receiver Interrupts .....           | 42    |

| Clearing Interrupts .....                    | 42    |

| <b>Chapter 5: Theory of Operation</b>        |       |

| Introduction .....                           | 43    |

| Interface Registers .....                    | 43    |

| Register Control .....                       | 44    |

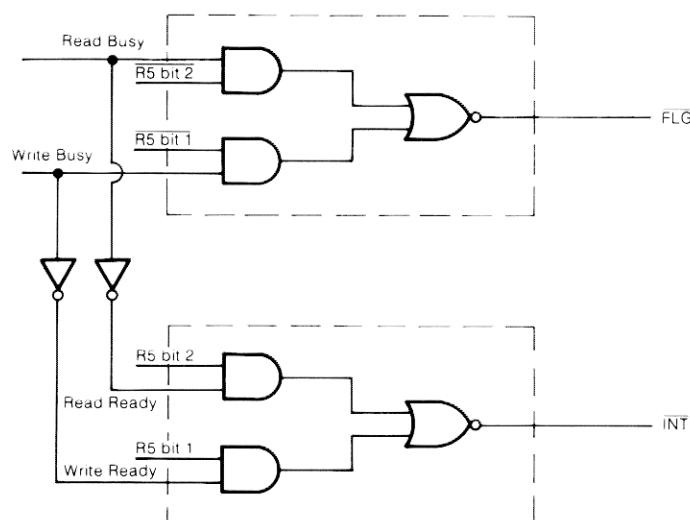

| Flag Signals .....                           | 44    |

| Interrupt Circuits .....                     | 45    |

| Clock Generator .....                        | 46    |

| I/O Drivers - Receivers .....                | 46    |

| Setting Registers .....                      | 46    |

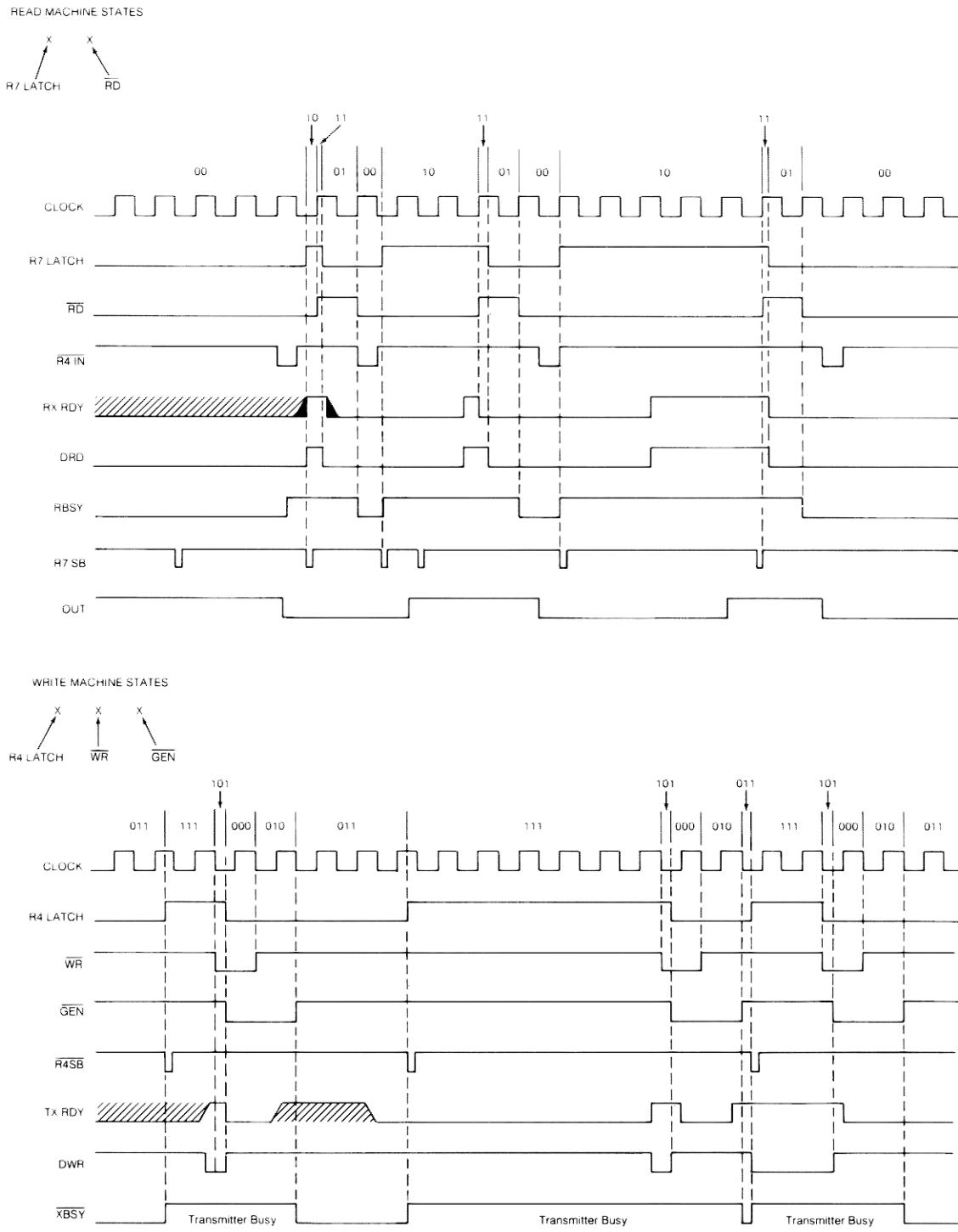

| Transmitting Data .....                      | 48    |

| Receiving Data .....                         | 48    |

| Reset .....                                  | 48    |

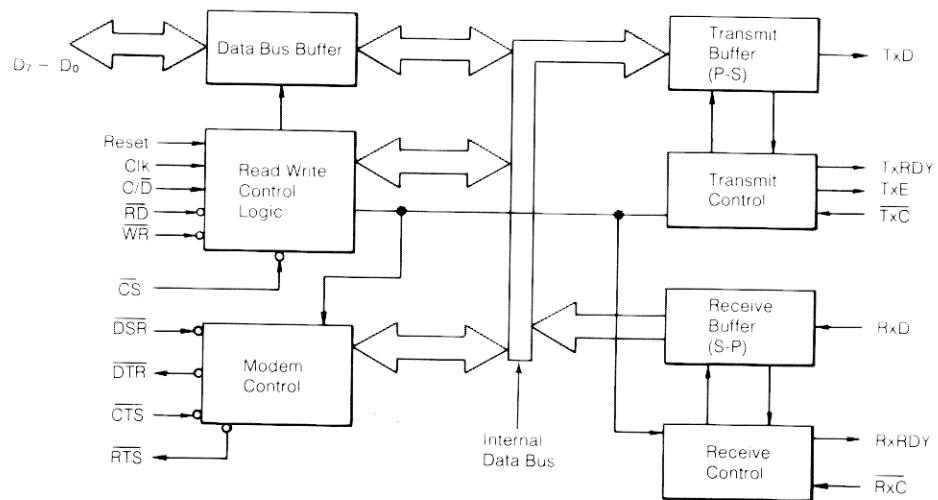

| The USART .....                              | 49    |

| <b>Chapter 6: Troubleshooting and Repair</b> |       |

| Introduction .....                           | 51    |

| Recommended Equipment .....                  | 51    |

| Test Programs .....                          | 51    |

| Troubleshooting .....                        | 52    |

| Broken Trace Repair .....                    | 52    |

| Replaceable Parts .....                      | 53    |

| <b>Appendix A</b>                            |       |

| System 45A Programming Notes .....           | 55    |

| 9825A Systems Programming ROM Notes .....    | 55    |

| Example Program .....                        | 56    |

| <b>Appendix B</b>                            |       |

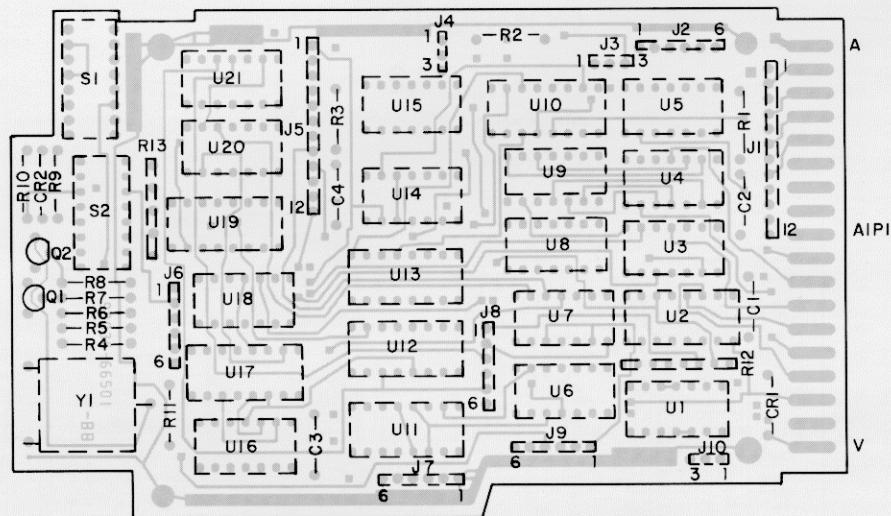

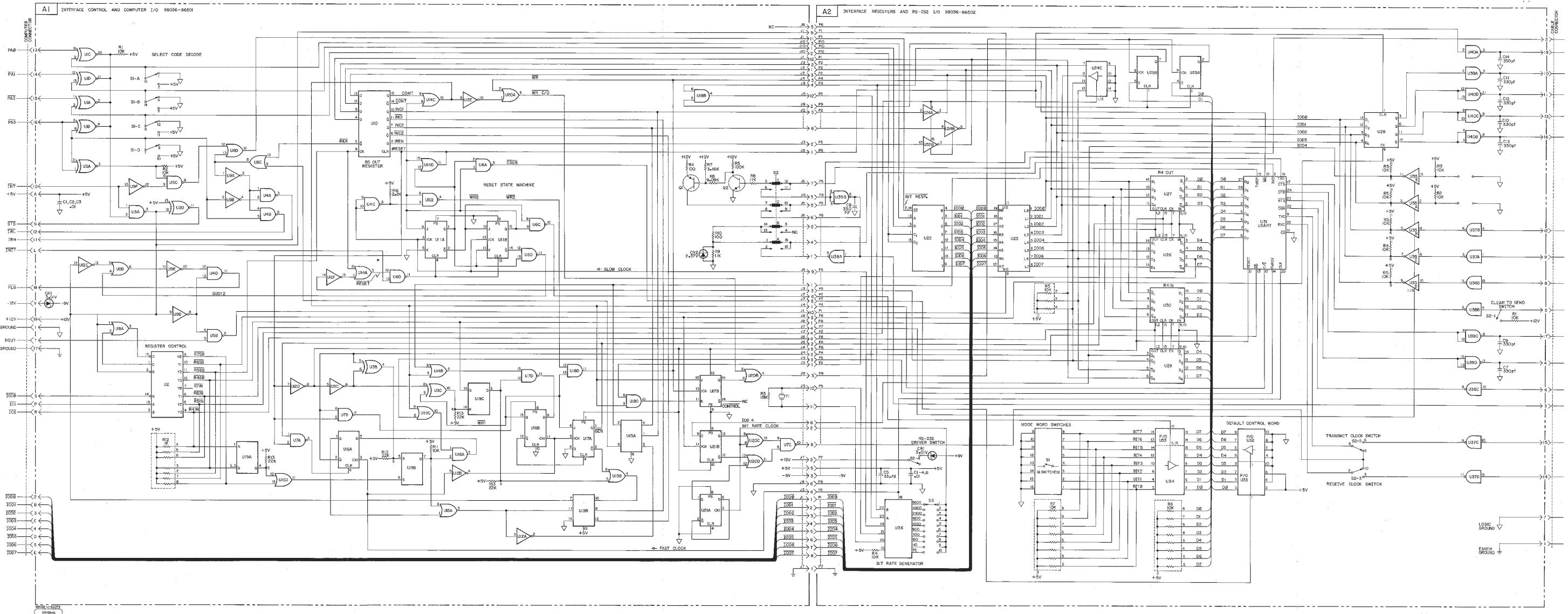

| Component Locators .....                     | 57,58 |

| Schematic Diagrams .....                     | 59    |

# Chapter 1

## General Information

### Manual Introduction

This manual describes the installation and operation of the HP 98036A Serial I/O Interface when used with an HP Desktop Computer and a data communications device. Theory of operation and troubleshooting chapters are also included to provide servicing information.

Complete background information about serial interfacing is provided by the Interfacing Concepts Manual for your Desktop Computer.

For those who are familiar with Hewlett-Packard interfaces and serial I/O, Chapters 2 and 4 provide sufficient hardware and programming information to enable you to "get on board" quickly.

### Chapter Summaries

- Chapter 1 describes the 98036A interface, the interface specifications, and the cable options available.

- Chapter 2 explains how to set the hardware configuration switches and how to install the interface.

- Chapter 3 describes the various I/O registers that are contained on the interface card.

- Chapter 4 explains how to program the interface. Examples show how to read the status, set mode and control words, and transmit and receive data.

- Chapter 5 contains the theory of operation.

- Chapter 6 provides troubleshooting and repair information.

- Appendix A contains example programming applications.

## 98036A Description

The HP 98036A Serial I/O Interface allows the computer to communicate with serial **asynchronous** data communication devices. The 98036A is equipped with both RS-232C and 20ma current loop drivers and receivers for the data transmitter and receiver. Data can be transferred at bits rates of 75 to 9600 bits per second. The interface is capable of **asynchronous** communication. A universal receiver/transmitter integrated circuit (USART) is used to manipulate data and provide the basic hardware protocol for **asynchronous** operation. The I/O ROM must be installed in the computer in order to use the interface. The interface is available with two cable configurations to allow the computer to act as a data terminal or the digital portion of a modem.

## Specifications

|                                            |                                                                       |

|--------------------------------------------|-----------------------------------------------------------------------|

| Power Requirements:<br>(from the computer) | +5 Volts at 300ma typ. 400 max.<br>±12 Volts at 20ma typ. 40 max      |

| Operating Temperature Range:               | 0°C to 45°C                                                           |

| Bit Rates:                                 | 9600, 4800, 2400, 1800, 1200, 600, 300, 150, 110, and 75 bits/second. |

| Mode of Operation:                         | <b>Asynchronous</b>                                                   |

| Data Buffer:                               | Transmitter-one character<br>Receiver-one character                   |

| Dimensions:                                | Approximately 16.3x8.9x3.8cm (6.4x3.5x1.5 inches)                     |

| Net Weight:                                | 4.16kg (1 lb. 14 oz)                                                  |

| Cable Length:                              | 2 metres (6.5 ft.)                                                    |

## Cable Options

The 98036A interface is available in three cable configurations: standard, Option 001 and Option 002.

The interface can be ordered for specific Desktop Computers by specifying the appropriate ordering option. See the following table.

| Cable Configuration | Ordering Option |           |           |

|---------------------|-----------------|-----------|-----------|

|                     | System 25       | System 35 | System 45 |

| Standard            | Standard        | 335       | 445       |

| Option 001          | 001             | 301       | 401       |

| Option 002          | Not Available   | 302       | 402       |

For example, to order a standard interface for a System 45, specify ordering Option 445.

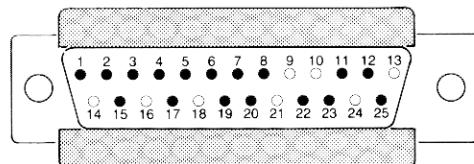

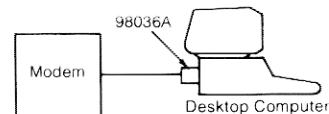

The standard 98036A Interface cable is shipped with a 2 metre (6.5 ft.) cable terminated with a standard female EIA 25 pin connector. The standard interface is connected between the computer and a data terminal.

Standard Cable Connector

Using the standard interface cable, the computer takes the place of a modem or computer communicating with a terminal.

Using Normal Data Communications

Using Desktop Computer/98036A(Standard)

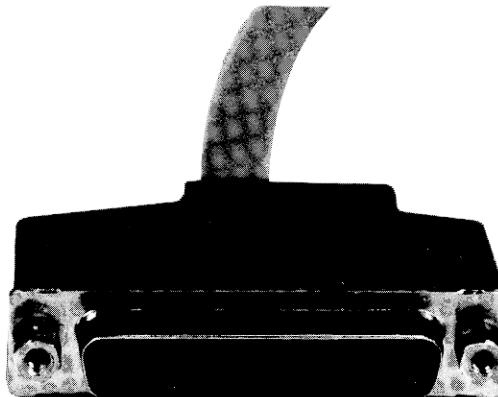

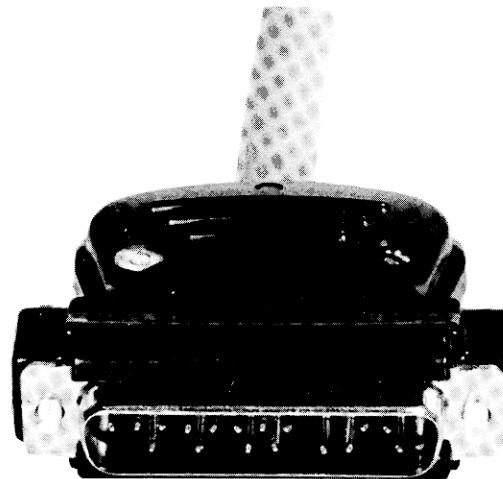

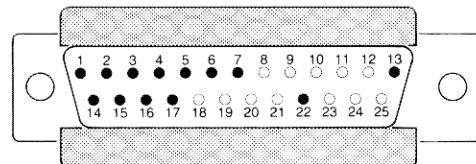

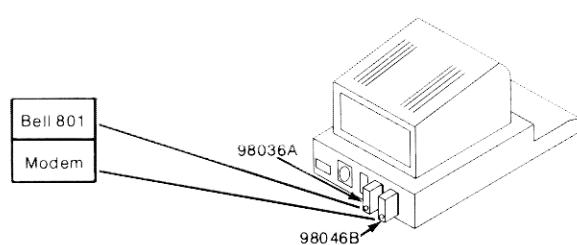

The 98036A Options 001 and 002 Interface cables are shipped with a 2 metre (6.5 ft.) cable terminated with a standard male EIA 25 pin connector. The following drawings show the differences between the Option 001 and 002 cables.

Cable Connector

Option 001

Option 002

Using the Option 001 interface cable, the computer acts as a data terminal connected to a modem.

Data

Channel

Using Normal Data Communications

Data

Channel

Using Desktop Computer/98036A (Option 001)

Using Desktop Computer/98036 (Option 002)

**NOTE**

The Option 002 interface cable is used ONLY with the optional Distributed System Software for System 35/45 desktop computers. No register control/access should be attempted for Option 002 interfaces. See your software manual for Option 002 interface programming details.

Here is a list of the signal lines and the corresponding connector pin numbers used in the standard and option 001 cables.

**Table 1. Cable Signals**

| DCE (Standard)              |              | RS232-C   |       |                                     | DTE (Option 001) |                        |

|-----------------------------|--------------|-----------|-------|-------------------------------------|------------------|------------------------|

| Register Access             | Standard Pin | Direction | Pin # | Signal Name                         | Option 001 Pin # | Register Access        |

| n.a.                        | 1            | ↔         | 1     | Protective Ground                   | 1                | n.a.                   |

| read                        | 3            | ←         | 2     | Transmitted Data                    | 2                | write                  |

| write                       | 2            | →         | 3     | Received Data                       | 3                | read                   |

| R4E, bit 7                  | 6            | ←         | 4     | Request to Send                     | 4                | R4D, bit 5<br>(Note 1) |

| R4D, bit 5                  | 4            | →         | 5     | Clear to Send                       | 5                | R4E, bit 7             |

| R4D, bit 1                  | 17           | →         | 6     | Data Set Ready                      | 6                | n.a.                   |

| n.a.                        | 7            | →         | 7     | Logic Ground                        | 7                | R6 IN, bit 0           |

| R6 OUT, bit 0               | 16           | →         | 8     | Carrier Detect                      | 8                | n.a.                   |

| n.a.                        | —            | —         | 9     | (Reserved for test)                 | —                | n.a.                   |

| n.a.                        | —            | —         | 10    | (Reserved for test)                 | —                | n.a.                   |

| n.a.                        | —            | ↔         | 11    | Data Rate Select (U.K.)<br>(Note 2) | 11               | R6 OUT, bit 2          |

| R6 OUT, bit 1               | 13           | →         | 12    | Second Carrier Detect               | 12               | R6 IN, bit 2           |

| n.a.                        | —            | →         | 13    | Second CTS                          | —                | n.a.                   |

| n.a.                        | —            | ↑         | 14    | Second TXD                          | —                | n.a.                   |

| n.a.                        | —            | →         | 15    | Transmitter Clock                   | 15               | (Note 3)               |

| n.a.                        | —            | →         | 16    | Second RXD                          | —                | n.a.                   |

| n.a.                        | —            | →         | 17    | Receiver Clock                      | 14               | (Note 3)               |

| n.a.                        | —            | —         | 18    | —                                   | —                | n.a.                   |

| R6 IN, bit 0<br>(Notes 1,4) | 8            | ↑         | 19    | Second RTS                          | 16               | R6 OUT, bit 0          |

| 5                           | —            | ↑         | 20    | Data Terminal Ready                 | 17               | R4D, bit 1             |

| R6 OUT, bit 2               | 11           | →         | 21    | Signal Quality Detect               | —                | n.a.                   |

| R6 OUT, bit 3               | 10           | →         | 22    | Ring Indicator                      | 9                | R6 IN, bit 1           |

| R6 IN, bit 1                | 9            | ↑         | 23    | Data Rate Select                    | 13               | R6 OUT, bit 1          |

| n.a.                        | —            | ↑         | 24    | Transmit clock (term)               | —                | n.a.                   |

| n.a.                        | —            | ↑         | 25    | —                                   | 10               | n.a.                   |

Note 1: this line cannot be read

Note 2: this line unassigned by RS-232-C

Note 3: switch selectable on 98036A

Note 4: can be set high by switch on 98036A

## Chapter 2

# Installation

## Introduction

Before installing the interface in your Desktop Computer it will be necessary to configure the interface for your particular application. Two methods are provided for interface configuration: hardware (switches) and software (program control). The hardware configuration switches determine the preset state of the interface when power is first applied or the computer is reset. Software configuration enables you to change the state of the mode and control words from within a program. The mode and control words remain in this configuration until either a new program statement changes them, the computer is reset, or power is switched off.

## Hardware Configuration (Exterior Access)

The following hardware configuration switches cannot be changed from within a program but interface disassembly is not required for access to these switches.

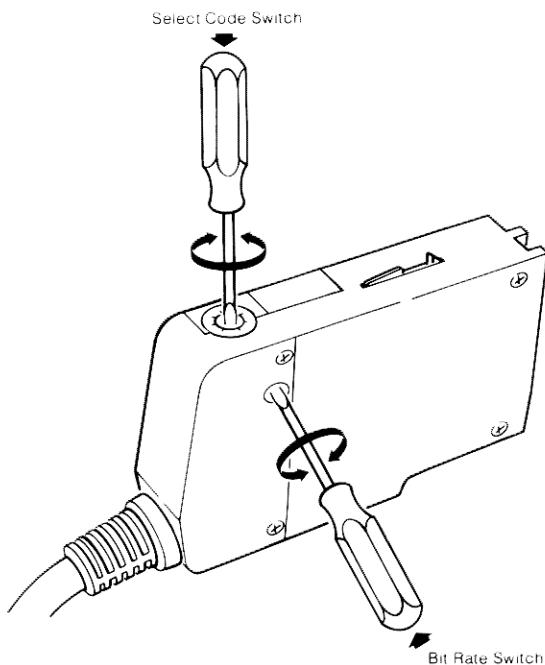

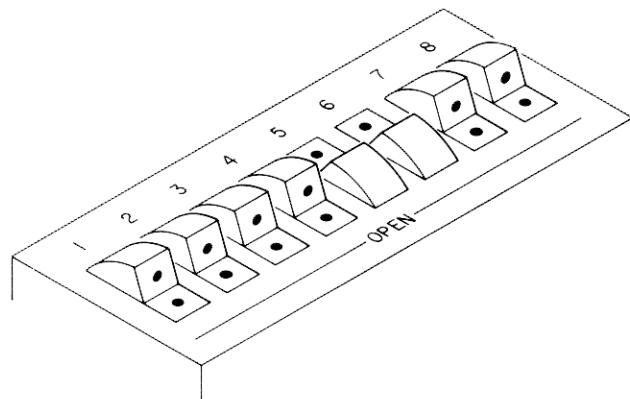

### Bit Rate (or Baud) Switch

The bit rate can be changed through the access hole in the side of the interface (see the next drawing). Set the bit rate switch to correspond to the bit rate of the data communications device connected to the interface. The following table shows the bit rates provided and the corresponding switch positions. Rotate the switch to the desired position with a small screwdriver.

| Switch Position | Bit Rate |

|-----------------|----------|

| 1               | 9600     |

| 2               | 4800     |

| 3               | 2400     |

| 4               | 1800     |

| 5               | 1200     |

| 6               | 600      |

| 7               | 300      |

| 8               | 150      |

| 9               | 110      |

| 0               | 75       |

} Use 1/16 Bit Resolution

} Use 1/64 Bit Resolution

## Select Code Switch

The interface select code switch is changed through the access hole provided in the top of the interface. The standard and Option 002 interfaces are preset at the factory to a select code of 10. The Option 001 interface is preset at the factory to a select code of 11. The select code should be checked for the proper setting as required by your system. Each interface must be set to a different select code. The Desktop Computer reserves certain select codes for its own internal peripherals. The Owners Manual supplied with your Desktop Computer lists the select code settings that may be used. To change the select code, use a small screwdriver and turn the switch to the desired setting (see the following drawing).

## Hardware Configuration (Interior Access)

The following hardware configuration switches set the default status of the USART mode word. Control of the following is provided by the USART mode word:

- Number of stop bits.

- Parity type.

- Enable-Disable parity.

- Character length.

- Bit Resolution.

**NOTE**

Although you can configure the USART mode word with register I/O program statements, the USART mode word is set to the default condition whenever power is applied, the computer is reset, or an interface reset is executed.

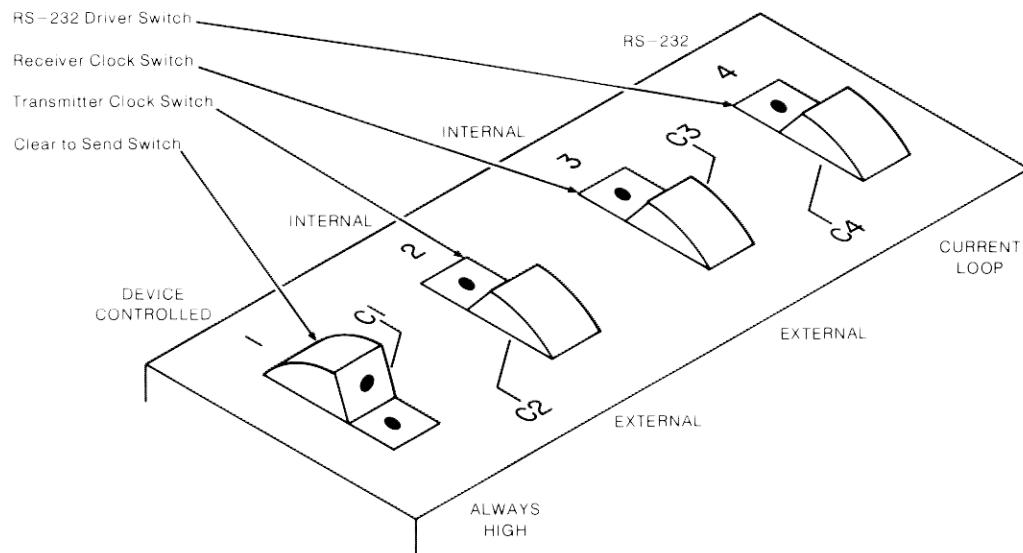

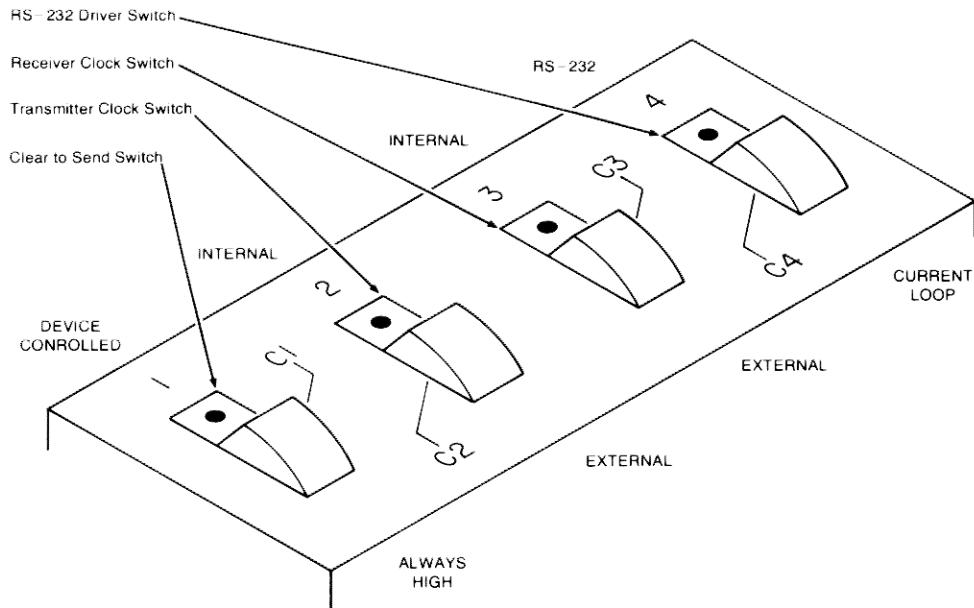

The interface MUST be disassembled in order to gain access to the USART mode word configuration switches. The following switches also require interface disassembly for access:

- I/O Mode Switch

- Driver Power Switch

- Receiver Clock Switch

- Transmitter Clock Switch

- Clear To Send Line Switch

The following table shows the factory settings for all interface configuration switches.

| Interface Configuration Switches | Factory Setting   | Can be changed from software | Disassembly required to change setting |

|----------------------------------|-------------------|------------------------------|----------------------------------------|

| Select Code                      |                   |                              |                                        |

| Standard Cable                   | 10                | No                           | No                                     |

| Option 001 Cable                 | 11                | No                           | No                                     |

| Option 002                       | 10                | No                           | No                                     |

| Bit Rate                         | 300               | No                           | No                                     |

| I/O mode Switch                  | RS-232            | No                           | Yes                                    |

| Driver Power Switch              | RS-232            | No                           | Yes                                    |

| Receiver Clock Switch            | Internal          | No                           | Yes                                    |

| Transmitter Clock Switch         | Internal          | No                           | Yes                                    |

| Clear to Send Line Switch        |                   |                              |                                        |

| Standard                         | Always High       | No                           | Yes                                    |

| Option 001                       | Always High       | No                           | Yes                                    |

| Option 002                       | Device Controlled | No                           | Yes                                    |

| Stop Bits                        | 2                 | Yes                          | Yes(default)                           |

| Parity                           | Disabled          | Yes                          | Yes(default)                           |

| Character Length                 | 8                 | Yes                          | Yes(default)                           |

| Bit Resolution                   | 1/64              | Yes                          | Yes(default)                           |

Instructions for setting these switches and the USART mode switches are provided following the next section.

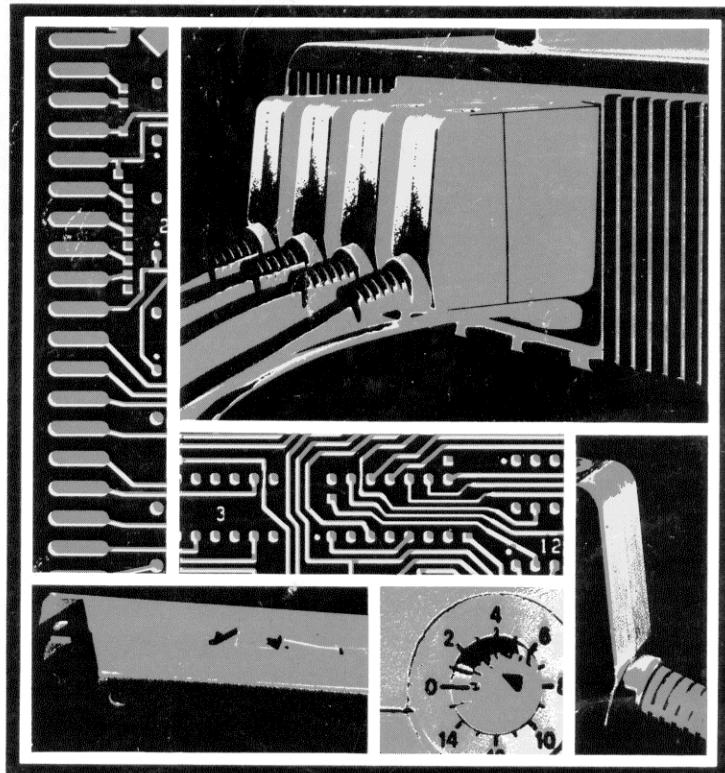

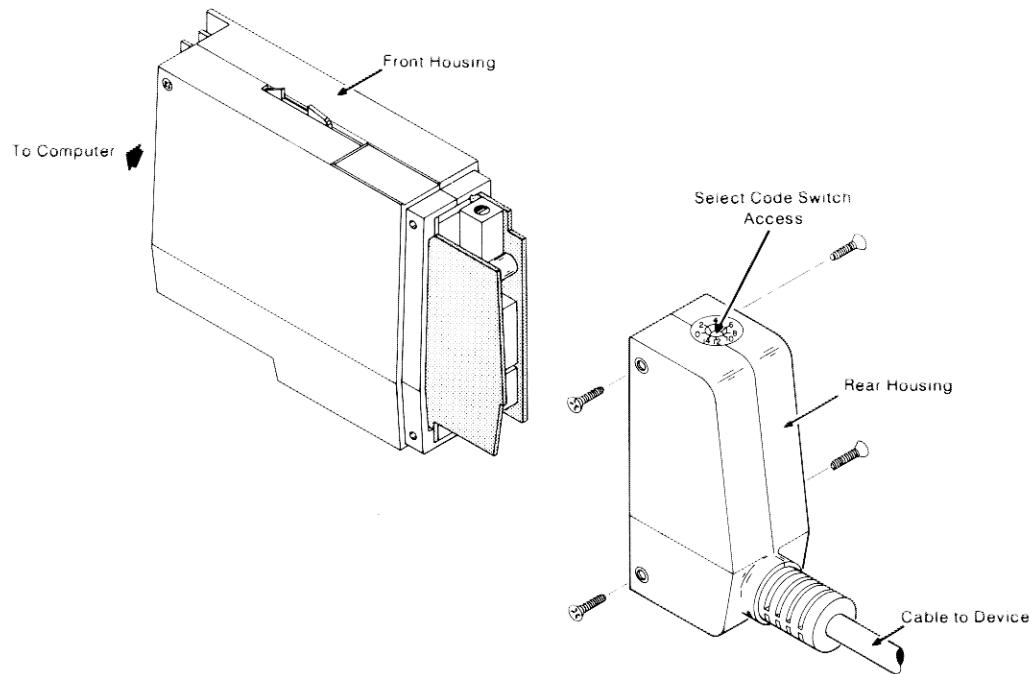

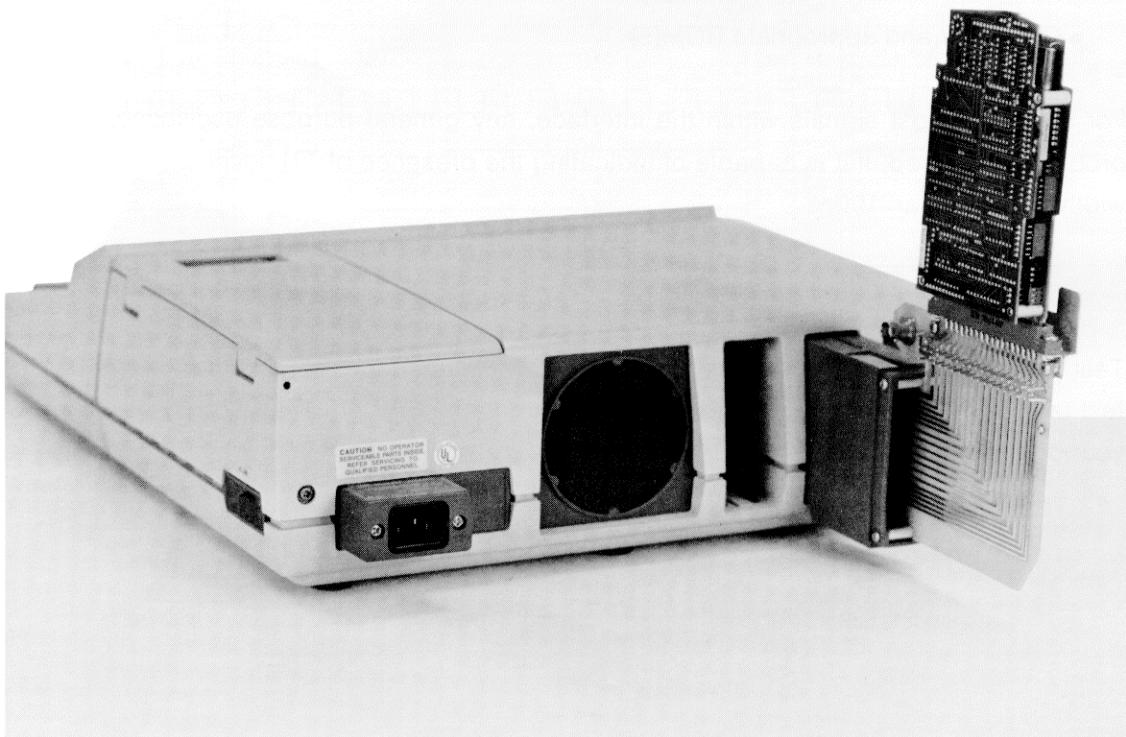

## Interface Disassembly

This section describes how to disassemble the interface. To disassemble the interface, use the procedure outlined below and refer to Figure 1.

- Remove the four screws that hold the rear housing to the front housing.

- Pull the rear housing off the front housing slightly, disconnect the cable connector from the PC assembly and remove the rear housing.

- Remove the four remaining screws in the front housing and separate the front housing cases.

- Carefully separate the printed circuit assemblies.

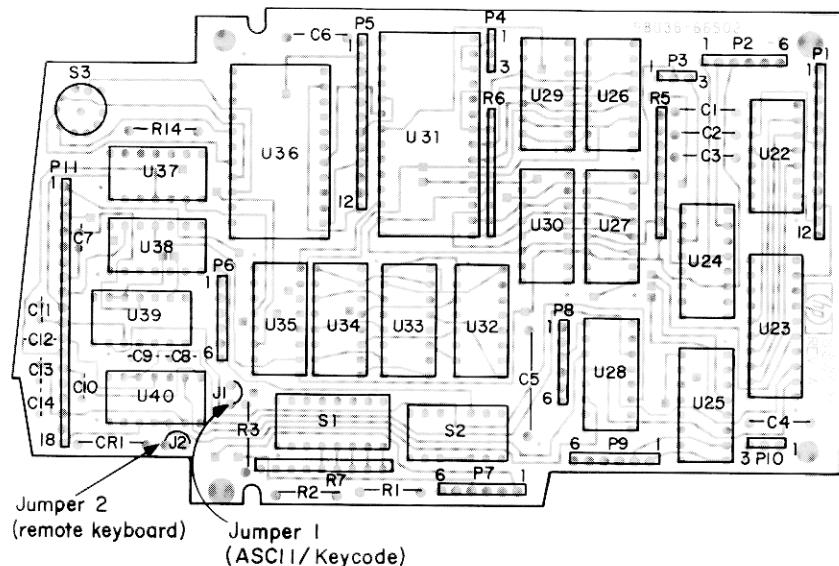

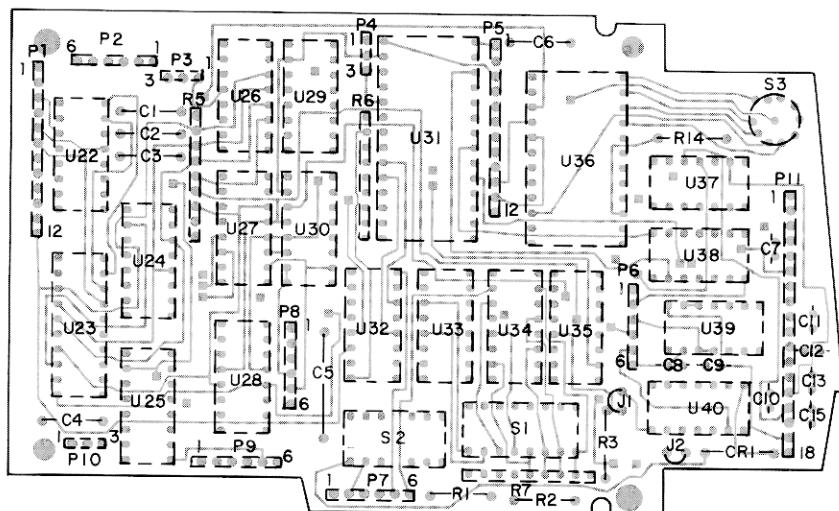

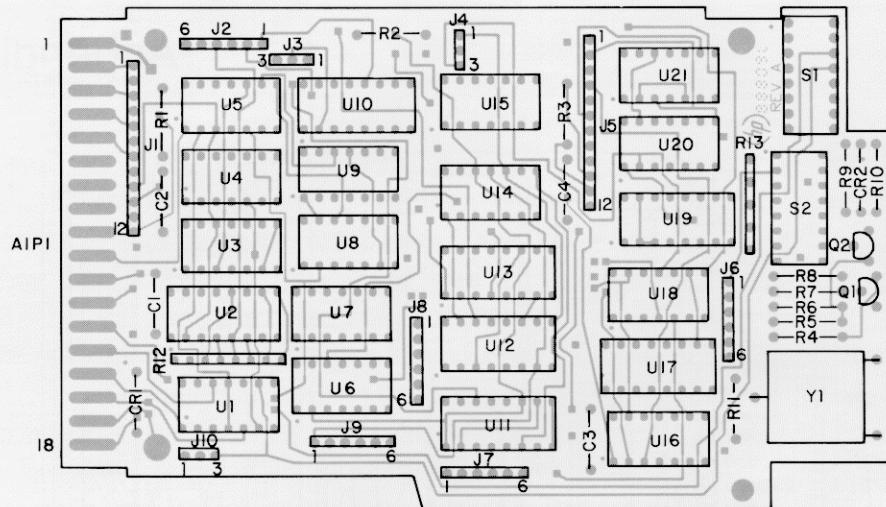

- See Figure 2 for the various switch locations.

- After setting the switches, reverse this procedure to assemble the interface. Be sure that the pins on the A2 assembly are properly seated in the connectors on the A1 assembly.

Figure 1. Interface Disassembly

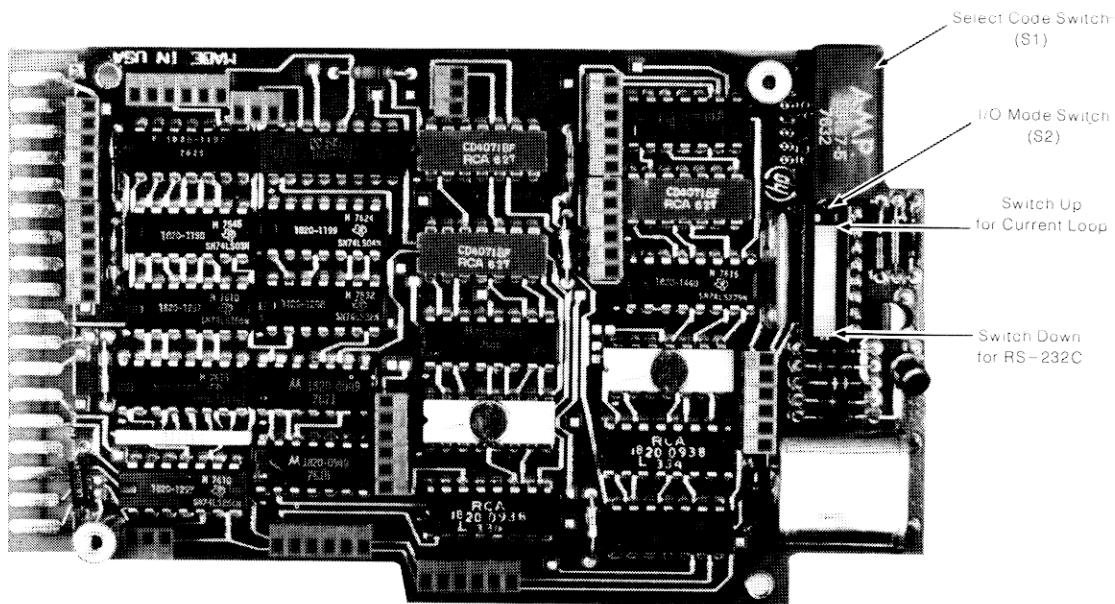

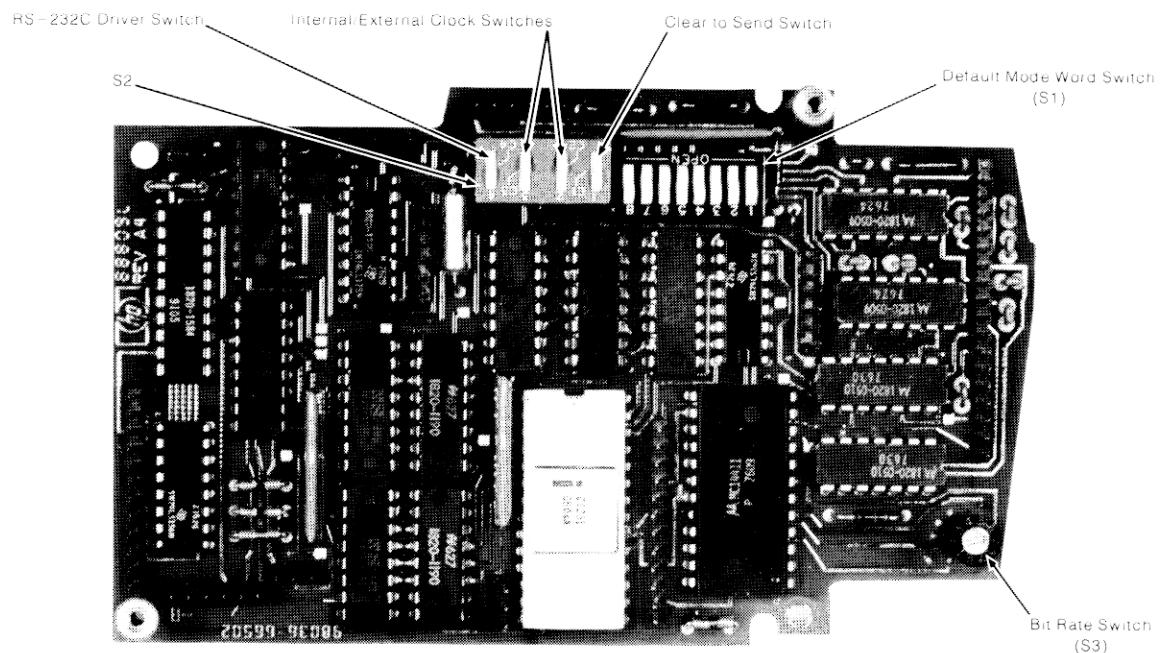

Figure 2. Interface Configuration Switches

Figure 2.(cont.)

## Setting The Switches

This section describes how to set the interface configuration switches for your particular requirements.

The following questions will help you determine how the interface switches should be set.

- What is the number of bits per character?

- Will parity be used?

- Even or odd parity?

- How many stop bits will be used?

- What bit resolution will be used?

- Will the operation be RS-232C or current loop?

- Will the internal clock be used for the transmitter and receiver clock?

- Does your data communications device provide the clear to send line (option 001 cable)?

- Does your data communications device provide the data terminal ready line (standard cable)?

### Mode Word Switches

The mode word switches (see figure 2) determine the default mode word used by the interface. The mode word determines the mode of interface operation. The default mode word is used when power is applied to the interface or when the interface or computer is reset. The default mode word can be overridden by subsequent mode words from the computer. Here is a description of each mode word bit position.

Any switch set to the open position sets the switch to a logical 1 (high). Any switch set to the opposite position sets the switch to a logical 0 (low).

Bits 7 and 6 — Determine the number of stop bits used.

Bit 5 — Determines whether odd or even parity is to be used (when parity is enabled).

Bit 4 — Enables or disables parity.

Bits 3 and 2 — Indicate how many bits per character (character length).

Bits 1 and 0 — Determine the bit resolution. Characters can be transferred at either the rate of the bit rate clock, or 1/16 the rate of the bit rate clock, or 1/64 the rate of the bit rate clock. The 1/64 position is recommended for increased immunity to signal distortion.

---

#### NOTE

Do not use the 1/64 bit resolution setting when the bit rate is set to 4800 or 9600 bits per second. Use the 1/16 bit resolution.

---

---

#### NOTE

Setting bits 1 and 0 both to zeros will result in erroneous interface operation. Do not operate the interface with bits 1 and 0 of the mode word both set to zero.

---

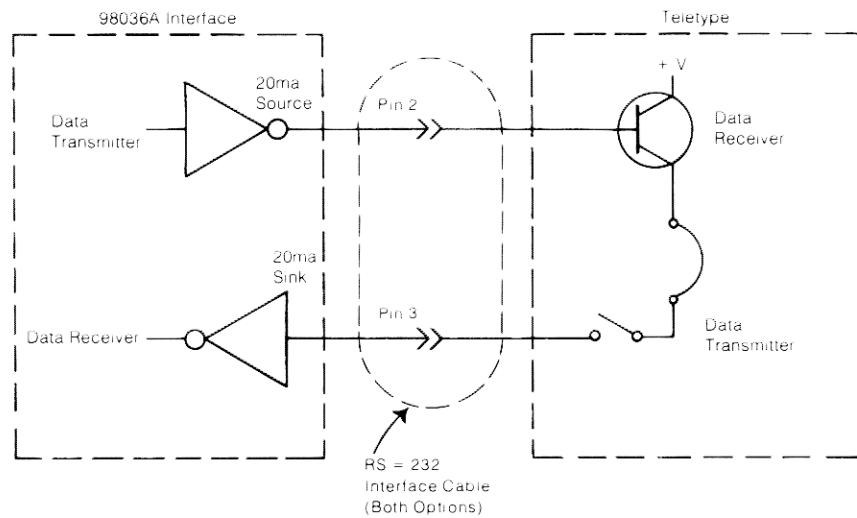

## Input/Output Mode Switch

Set the I/O mode switch (See Figure 2) for either RS-232C or 20ma current loop operation depending on the device to be connected to the interface.

The RS-232C position is used when the interface is to be connected to a RS-232C compatible data terminal or modem.

The 20ma current loop position is used when the interface is to be connected to some teletype terminals. Only the transmit data and receive data lines are switched in current loop operation. The RS-232C control signals are not available in the current loop mode.

The following diagram shows a typical current loop connection.

## RS-232C Driver Switch

The RS-232C driver switch MUST be set to the same position as the I/O mode switch. If the I/O mode switch is set for RS-232C operation, then the RS-232C driver switch MUST be set to the RS-232C position. If the I/O mode switch is set for current loop operation, then the RS-232C driver switch MUST be set to the current loop position.

## Internal/External Clock Switches

External transmit and receive clocks may be used instead of the internal bit rate clock. This feature is not usually used for asynchronous operation. The external clock should have a 50% duty cycle, and be sure that the interface bit resolution is the same as the external clock resolution.

When either the transmit or receive clock switch is set to the internal position, the internal bit rate clock is used. When either the transmit or receive clock switch is in the external position, an appropriate external clock must be input to the interface. See Table 1 for the cable signal line numbers.

## Clear to Send Switch

If the device connected to the interface does not provide the clear to send signal (data terminal ready line), set the clear to send switch to the 'always high' position. If the device does provide the clear to send signal, set the switch to the 'device controlled' position.

Factory Preset Switch Positions for Standard and Option 001

Factory Preset Switch Positions for Option 002

## Interface Installation

After the interface configuration switches have been set, assemble the interface housing by reversing the disassembly procedure. Be sure that the pins on the A2 assembly are properly seated in the connectors on the A1 assembly. With the computer switched off, install the interface into any one of the I/O slots on the back of the computer. Connect the other end of the interface cable to an applicable data communications device (e.g., data terminal, modem).

## Chapter 3

# The Interface Registers

## Introduction

This chapter describes the contents of the various 98036A interface registers. Access to these registers is described in Chapter 4. The 98036A interface is controlled by I/O ROM statements. When writing to and reading from the interface, internal interface registers (R4, R5, and R6) are written into, and read from, to control and monitor the interface operation. All registers are 8-bits long. Each register bit enables or disables an interface function or operation. In the following description of the registers, notice that some of the R4 and R6 bit definitions are different depending on whether the standard or the option 001 cable is used. Option 002 bit definitions are not shown.

## Bit Position Values

Each 8-bit register (R4, R5, or R6) has a decimal value assigned to each bit. To set a bit in a register, you add the decimal value for that bit to your register I/O statement value. For example, to set bit 4 to a 1, the value specified is decimal 16 (see the following drawing).

| Bit Position  | BIT 7 | BIT 6 | BIT 5 | BIT 4 | BIT 3 | BIT 2 | BIT 1 | BIT 0 |

|---------------|-------|-------|-------|-------|-------|-------|-------|-------|

| Decimal Value | 128   | 64    | 32    | 16    | 8     | 4     | 2     | 1     |

To set bits 5, 4, and 1, add the values of those bits and specify the result (i.e.,  $32 + 16 + 2 = 50$ ).

In this manner, any bit or combination of bits can be set in the R4, R5, or R6 registers.

When writing into a register, all the register bits are accessed. Thus when changing a bit in a register, the entire register word must be sent. For example, setting only bit 3 of a register will clear all the other bits of that register. Always send the sum total value of a register when setting or changing a register.

## R4 Registers

There are two R4 registers (R4OUT and R4IN). All communication between the computer and the USART passes through either R4OUT or R4IN. Transmit data, the USART mode word, and the USART control word are sent through the R4OUT register while received data and the USART status word are entered through the R4IN register. With this in mind, the R4 registers can be thought of as five distinct pseudo-registers (R4A through R4E). Here are the functions provided by the R4 registers:

| Function           | Register Used | Pseudo Register |

|--------------------|---------------|-----------------|

| Data Output        | R4OUT         | R4A             |

| Data Input         | R4IN          | R4B             |

| USART Mode Word    | R4OUT         | R4C             |

| USART Control Word | R4OUT         | R4D             |

| USART Status Word  | R4IN          | R4E             |

### Transmit Data Register (R4A)

Each character sent from the computer enters this register before it is sent serially to the data communications device. A register I/O operation is used to output characters from the computer to this register through R4OUT. All 8-bits of the transmit data register are used for the data character.

### Received Data Register (R4B)

Serial data received from a data communications device is assembled into an 8-bit character before it is input by the computer. A register I/O operation from the computer is used to input a character from this register through R4IN. All 8-bits of the received data register are used for the data character.

---

#### NOTE

The USART mode and control words allow configuration of the 98036A via program control. These words are set to the default conditions when power is applied or the computer is reset. They can be changed under program control.

---

## The USART Mode Word (R4C)

The mode word determines the mode of operation of the interface. A mode word is sent to the interface using register I/O statements from the computer. A mode word from the computer overrides the default mode word that was set (from the default mode word switches) during an interface reset. Here is a description of the USART mode word bit positions.

| USART Mode Word Bit Descriptions |              |              |              |             |                  |             |                        |                       |

|----------------------------------|--------------|--------------|--------------|-------------|------------------|-------------|------------------------|-----------------------|

| Most Significant Bit             | BIT 7        | BIT 6        | BIT 5        | BIT 4       | BIT 3            | BIT 2       | BIT 1                  | Least Significant Bit |

| Number of Stop Bits              |              |              |              |             | Character Length |             | Bit Rate Factor        |                       |

| 00=not valid                     |              |              |              |             | 00=5 bits        |             | 00=not used            |                       |

| 01=1 bit                         |              |              | Parity Type  | 0=Odd       | 01=6 bits        |             | 01=1×bit rate clock    |                       |

| 10=1.5 bits                      |              |              |              | 1=Even      | 10=7 bits        |             | 10=1/16×bit rate clock |                       |

| 11=2 bits                        |              |              |              |             | 11=8 bits        |             | 11=1/64×bit rate clock |                       |

| BIT VALUE=128                    | BIT VALUE=64 | BIT VALUE=32 | BIT VALUE=16 | BIT VALUE=8 | BIT VALUE=4      | BIT VALUE=2 | BIT VALUE=1            |                       |

Bits 7 and 6 — Determine the number of stop bits used.

Bit 5 — Determines whether odd or even parity is to be used (if parity is enabled).

Bit 4 — Enables or disables parity.

Bits 3 and 2 — Indicates the number of bits per character (character length).

Bits 1 and 0 — Determine the rate at which characters will be transferred. Characters can be transferred at either the rate of the bit rate clock, or 1/16 the rate of the bit rate clock, or 1/64 the rate of the bit rate clock. The 1/64 position is recommended for increased immunity to signal distortion.

---

### NOTE

Do not use the 1/64 bit resolution setting when the bit rate is set to 4800 or 9600 bits per second. Use the 1/16 bit resolution.

---

---

### NOTE

Setting bits 1 and 0 both to zeros will result in erroneous interface operation. Do not operate the interface with bits 1 and 0 of the mode word both set to 0.

---

## The USART Control Word (R4D)

The USART is the integrated circuit in the interface that transmits and receives data in the proper format. The USART control word is accessed when bit 0 of the R5OUT register is a one. The USART control word is output from the computer with register I/O statements. Here is a description of the USART control word bit positions.

| Most Significant Bit |             |                                                                     |                                        |                      |                      |                                                                           |                         | Least Significant Bit |                |                |                |               |               |               |               |

|----------------------|-------------|---------------------------------------------------------------------|----------------------------------------|----------------------|----------------------|---------------------------------------------------------------------------|-------------------------|-----------------------|----------------|----------------|----------------|---------------|---------------|---------------|---------------|

| BIT 7                | BIT 6       | BIT 5                                                               | BIT 4                                  | BIT 3                | BIT 2                | BIT 1                                                                     | BIT 0                   | BIT 7                 | BIT 6          | BIT 5          | BIT 4          | BIT 3         | BIT 2         | BIT 1         | BIT 0         |

| Always 0             | USART Reset | Clear To Send Pin 5(Standard)<br>Request To Send Pin 4 (Option 001) | Reset Status Bits of USART Status Word | Send Break Character | Enable Data Receiver | Data Set Ready Pin 6(Standard)<br>Data Terminal Ready Pin 20 (Option 001) | Enable Data Transmitter | BIT VALUE = 128       | BIT VALUE = 64 | BIT VALUE = 32 | BIT VALUE = 16 | BIT VALUE = 8 | BIT VALUE = 4 | BIT VALUE = 2 | BIT VALUE = 1 |

Bit 7 — Bit 7 is not used and must always be a 0.

Bit 6 — Is used to reset the USART. When bit 6 is a 1, the USART is forced into an idle mode. The next byte sent to the interface will be accepted as a USART mode word.

Bit 5 — This is a programmable RS-232C signal. In the case of the standard cable, the signal is sent to the device on the Clear To Send line (pin 5). In the case of the option 001 cable, the signal is sent to the device on the Request To Send line (pin 4).

Bit 4 — Resets status bits 3, 4, and 5 of the USART status word to 0.

Bit 3 — Enables the USART to output a "break" to the data communications device. This causes a continuous space to be output. The "break" signal is not automatically terminated. Your software must reset the "break" signal.

Bit 2 — When this bit is a 1, it allows the interface to receive characters for transfer to the computer.

Bit 1 — For the standard cable, when bit 1 is a 1, a Data Set Ready signal is sent to the data terminal of pin 6 of the terminal connector. For the option 001 cable, when bit 1 is a 1, a Data Terminal Ready signal is sent to the modem on pin 20 of the modem connector.

Bit 0 — The USART transmitter is enabled when this bit is a 1.

### NOTE

The power-up default control word is 5. Bits 0 and 2 are set.

## The USART Status Word (R4E)

The status word can be accessed when bit 0 of R5OUT is a 1. A read binary statement from the computer is used to input the status word to the computer. Here is a description of the USART status word bit positions.

| Most Significant Bit                                                          |          |                  |                  |                 |                      |                   |                      | Least Significant Bit |              |              |              |             |             |             |             |

|-------------------------------------------------------------------------------|----------|------------------|------------------|-----------------|----------------------|-------------------|----------------------|-----------------------|--------------|--------------|--------------|-------------|-------------|-------------|-------------|

| BIT 7                                                                         | BIT 6    | BIT 5            | BIT 4            | BIT 3           | BIT 2                | BIT 1             | BIT 0                | BIT VALUE=128         | BIT VALUE=64 | BIT VALUE=32 | BIT VALUE=16 | BIT VALUE=8 | BIT VALUE=4 | BIT VALUE=2 | BIT VALUE=1 |

| Request To Send<br>Pin 4(Standard)<br>Data Set Ready<br>Pin 6<br>(Option 001) | Always 0 | Framing<br>Error | Overrun<br>Error | Parity<br>Error | Transmitter<br>Empty | Receiver<br>Ready | Transmitter<br>Ready |                       |              |              |              |             |             |             |             |

Bit 7 — Using the standard cable, bit 7 indicates the status of the Request To Send line, pin 4 of the terminal connector. Using the option 001 cable, bit 7 indicates the status of the Data Set Ready line, pin 6 of the modem connector.

Bit 6 — Not used, always 0.

Bit 5 — This bit is a 1 when the received data did not contain the proper number of stop bits or when a break has been received.

Bit 4 — This bit is a 1 when data is received before the data receiver buffer is empty (overrun error).

Bit 3 — This bit is a 1 when a parity error occurs.

Bit 2 — This bit is a 1 when the USART's data transmitter buffer is empty.

Bit 1 — This bit is a 1 when the USART's data receiver is ready with a received character.

Bit 0 — This bit is a 1 when the USART's data transmitter buffer is ready to transmit data.

## R5 Registers

There are two R5 registers. R5OUT holds the interface control word. The interface control word is sent to the R5OUT register using register I/O statements from the computer.

R5IN holds the interface status word. The interface status word is input by the computer from the R5IN register.

Here is a description of the R5OUT and R5IN bit positions.

### R5OUT Register

| Must: Significant Bit            |                |                                  |                |               |                                               |                                                  |                                                           | Least Significant Bit |  |

|----------------------------------|----------------|----------------------------------|----------------|---------------|-----------------------------------------------|--------------------------------------------------|-----------------------------------------------------------|-----------------------|--|

| BIT 7                            | BIT 6          | BIT 5                            | BIT 4          | BIT 3         | BIT 2                                         | BIT 1                                            | BIT 0                                                     |                       |  |

| Interface<br>Interrupt<br>Enable | —              | Programmed<br>Interface<br>Reset | —              | —             | Interrupt<br>Control 2<br>Receiver<br>Control | Interrupt<br>Control 1<br>Transmitter<br>Control | R4 Control<br>0 = Data IN<br>OUT<br>1 = Control<br>Status |                       |  |

| BIT VALUE = 128                  | BIT VALUE = 64 | BIT VALUE = 32                   | BIT VALUE = 16 | BIT VALUE = 8 | BIT VALUE = 4                                 | BIT VALUE = 2                                    | BIT VALUE = 1                                             |                       |  |

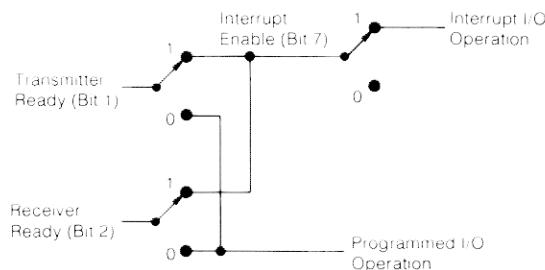

Bit 7 — When bit 7 is a 1, the interface is enabled to interrupt the computer's operation. Either bit 1 or bit 2 should be a 1 when bit 7 is a 1.

Bit 6 — Not used.

Bit 5 — When bit 5 is set to a 1, the interface is reset to the power up default condition. The power up default conditions are:

1. The default mode word will be used.

2. The USART control word is set to 5.

3. All other registers are set to 0.

Bit 5 is reset during the interface reset.

Bits 4 and 3 — Not used.

Bit 2 — Enables the interface's receiver for interrupt operation. When bit 2 is a 1 and the receiver is ready, an interrupt I/O operation will be performed (if bit 7 is also set). Bit 2 must be a 0 for normal programmed input operation.

Bit 1 — Enables the transmitter for interrupt operation. When bit 1 is a 1 and the transmitter is ready, an interrupt I/O operation will be performed (if bit 7 is also set). Bit 1 must be a 0 for normal programmed output operation.

Bit 0 — Determines whether the next transfer to or from the computer will be a data character or a control or status word. When bit 0 is a 1, access to the USART mode, status, and control words is enabled. With this access established, control words can be sent or changed and the USART status can be read. When bit 0 is a 0, data can be received or transmitted depending on how the USART control word was set.

#### NOTE

Bit 1 and bit 2 of R5OUT must be cleared for non-interrupt I/O operation.

## R5IN Register

| R5IN Register        |                                   |              |                           |                           |             |             |                                |                                   |

|----------------------|-----------------------------------|--------------|---------------------------|---------------------------|-------------|-------------|--------------------------------|-----------------------------------|

| Most Significant Bit |                                   |              |                           | Least Significant Bit     |             |             |                                |                                   |

| BIT 8                | BIT 7                             | BIT 6        | BIT 5                     | BIT 4                     | BIT 3       | BIT 2       | BIT 1                          | BIT 0                             |

| Peripheral Status 1  | Interface Interrupt Enable Status | 0            | Interface I.D. 0 Always 0 | Interface I.D. 1 Always 1 | 0           | 0           | Control Status 2 Receiver Mode | Control Status 1 Transmitter Mode |

| BIT VALUE=256        | BIT VALUE=128                     | BIT VALUE=64 | BIT VALUE=32              | BIT VALUE=16              | BIT VALUE=8 | BIT VALUE=4 | BIT VALUE=2                    | BIT VALUE=1                       |

Bit 8 — Is the interface status bit. This bit is always 1 when the interface is installed and operational in the computer.

Bit 7 — Is a 1 when the interface interrupt is enabled (bit 7 of R5OUT).

Bit 6 — Not used, always 0.

Bit 5 and 4 — Identify the interface as a serial interface. Bit 5 is always 0 and bit 4 is always 1.

Bits 3 and 2 — Not used, always 0.

Bit 1 — Is a 1 when the receiver interrupt control is enabled (bit 2 of R5OUT).

Bit 0 — Is a 1 when the transmitter interrupt control is enabled (bit 1 of R5OUT).

## R6 Registers

There are two R6 registers. The R6 registers are accessed by interface read and write operations.

R6OUT is controlled by the computer and is used to send control information to the data communications device. The contents of R6OUT are changed by a register I/O operation to the interface. The control information is then sent to the data communications device.

R6IN monitors the RS-232 status lines from the data communications device. The contents of the register are input to the computer by a register I/O operation.

Here is a description of the R6OUT and R6IN bit positions for both the standard and option 001 cables. Remember, when using the standard cable, the Desktop Computer/98036A Interface acts like a modem in communicating with a terminal and when using the option 001 cable, the Desktop Computer/98036A Interface acts like a terminal connected to a modem.

### R6OUT Register (standard cable)

| R6OUT Register (Standard Cable) |              |              |                                     |                       |                              |                                 |                           |

|---------------------------------|--------------|--------------|-------------------------------------|-----------------------|------------------------------|---------------------------------|---------------------------|

| Most Significant Bit            |              |              |                                     | Least Significant Bit |                              |                                 |                           |

| BIT 7                           | BIT 6        | BIT 5        | BIT 4                               | BIT 3                 | BIT 2                        | BIT 1                           | BIT 0                     |

| —                               | —            | —            | Half/Full Speed Control (Interface) | Ring Indicator Pin 22 | Signal Quality Detect Pin 21 | Secondary Carrier Detect Pin 12 | Data Carrier Detect Pin 8 |

| BIT VALUE=128                   | BIT VALUE=64 | BIT VALUE=32 | BIT VALUE=16                        | BIT VALUE=8           | BIT VALUE=4                  | BIT VALUE=2                     | BIT VALUE=1               |

Bits 7 thru 5 — Not used.

Bit 4 — This bit is used to signal the interface that either half or full speed data transfer is being done (see R6IN, bit 1). When bit 4 is a 0, normal bit rate clock speed is being used. When bit 4 is a 1, data transfer is half the switch selected bit rate clock speed. Bit 4 information is used internally by the interface.

Bit 3 — Normally indicates a ringing signal to the data terminal on pin 22 of the terminal connector when bit 3 is a 1. Since no ringing signal is involved in a standard cable application, this bit is not normally used, however it is available.

Bit 2 — Normally is used to indicate to the data terminal whether or not there is a high probability of an error in the data received by the modem. If bit 2 is a 1, the received data is probably in error. This signal is sent to the terminal on pin 21 of the terminal connector. Since no data channel is involved in a standard cable application, this bit is not normally used however it is available.

Bit 1 — Normally indicates to the data terminal that the secondary channel carrier is being sent, when bit 1 is a 1. This signal is sent to the data terminal on pin 12 of the terminal connector. The secondary channel in a standard cable application is a pseudo-channel since no carrier is involved.

Bit 0 — Normally indicates to the data terminal that the primary channel carrier is being received, when bit 0 is a 1. This signal is sent to the data terminal on pin 8 of the terminal connector. The primary channel in a standard cable application is a pseudo-channel since no carrier is involved.

## R6IN Register (standard cable)

| Most Significant Bit |              |              |              |             |             |                                |                                  | Least Significant Bit |

|----------------------|--------------|--------------|--------------|-------------|-------------|--------------------------------|----------------------------------|-----------------------|

| BIT 7                | BIT 6        | BIT 5        | BIT 4        | BIT 3       | BIT 2       | BIT 1                          | BIT 0                            |                       |

| Always 1             | Always 1     | Always 1     | Always 1     | Always 1    | Always 0    | Data Signal Rate Select Pin 23 | Secondary Request To Send Pin 19 |                       |

| BIT VALUE=128        | BIT VALUE=64 | BIT VALUE=32 | BIT VALUE=16 | BIT VALUE=8 | BIT VALUE=4 | BIT VALUE=2                    | BIT VALUE=1                      |                       |

Bits 7 thru 2 — Not used.

Bit 1 — This signal is sent to the interface from the data terminal on pin 23 of the terminal connector. This signal is used when the terminal has two data signalling rates or two ranges of data signalling rates. When bit 1 is a 1, the higher data signalling rate or range of rates is selected.

Bit 0 — This signal is sent to the interface from the data terminal on pin 19 of the terminal connector. When bit 0 is a 1, the secondary request to send line is raised high indicating to the interface that the terminal has information to send.

## R6OUT Register (option 001 cable)

| R6OUT Register (option 001 cable) |              |              |                         |                         |                                      |                                |                                  |

|-----------------------------------|--------------|--------------|-------------------------|-------------------------|--------------------------------------|--------------------------------|----------------------------------|

| Most Significant Bit              |              |              |                         | Least Significant Bit   |                                      |                                |                                  |

| BIT 7                             | BIT 6        | BIT 5        | BIT 4                   | BIT 3                   | BIT 2                                | BIT 1                          | BIT 0                            |

| —                                 | —            | —            | Half/Full Speed Control | Testing Purposes Pin 25 | Data Signal Rate Select (U.K.)Pin 11 | Data Signal Rate Select Pin 23 | Secondary Request To Send Pin 19 |

| BIT VALUE=128                     | BIT VALUE=64 | BIT VALUE=32 | BIT VALUE=16            | BIT VALUE=8             | BIT VALUE=4                          | BIT VALUE=2                    | BIT VALUE=1                      |

Bits 7 thru 5 — Not used.

Bit 4 — This bit is used to signal the interface that either half or full speed data transfer is in effect (see R6OUT, bit 1). When this bit is a 0, normal bit rate clock speed is being used. When bit 4 is a 1, data transfer is half the switch selected bit rate. Bit 4 information is used internally by the interface.

Bit 3 — Is used for testing purposes only. This bit is output to pin 25 of the modem connector.

Bit 2 — This signal is sent from the interface to the modem on pin 11 of the modem connector. Pin 11 is used in the United Kingdom for the Data Signal Rate Select signal. The signal is used to select between two data signalling rates or two ranges of data signalling rates. When bit 2 is a 1, the higher data signalling rate or range of data signalling rates of the modem is being requested.

Bit 1 — This signal is sent from the interface to the modem on pin 23 of the modem connector. Pin 23 is used for the Data Signal Rate Select signal. The signal is used to select between two data signalling rates or two ranges of data signalling rates. When bit 1 is a 1, the higher data signalling rate of the modem is requested.

Bit 0 — Is sent from the interface to the modem on pin 19 of the modem connector. When this signal is a 1, the Secondary Request to Send signal is sent to the modem indicating to the modem that the computer has information to send.

## R6IN Register (option 001 cable)

| R6IN Register (option 001 cable) |              |              |              |                       |                                 |                       |                           |

|----------------------------------|--------------|--------------|--------------|-----------------------|---------------------------------|-----------------------|---------------------------|

| Most Significant Bit             |              |              |              | Least Significant Bit |                                 |                       |                           |

| BIT 7                            | BIT 6        | BIT 5        | BIT 4        | BIT 3                 | BIT 2                           | BIT 1                 | BIT 0                     |

| Always 1                         | Always 1     | Always 1     | Always 1     | Always 1              | Secondary Carrier Detect Pin 12 | Ring Indicator Pin 22 | Data Carrier Detect Pin 8 |

| BIT VALUE=128                    | BIT VALUE=64 | BIT VALUE=32 | BIT VALUE=16 | BIT VALUE=8           | BIT VALUE=4                     | BIT VALUE=2           | BIT VALUE=1               |

Bits 7 thru 3 — Not used.

Bit 2 — The signal is sent to the interface from the modem on pin 12 of the modem connector. When bit 2 is a 1, it indicates that the secondary channel carrier is being received.

Bit 1 — This signal indicates to the interface that a ringing signal is being received by the modem when bit 1 is a 1. The signal is sent to the interface on pin 22 of the modem connector.

Bit 0 — This signal, Carrier Detect, indicates to the interface that the modem is receiving an acceptable signal, when bit 0 is a 1. This signal is sent to the interface on pin 8 of the modem connector.

# Chapter 4

## Talking to the Interface

### Introduction

This chapter describes how to program the 98036A interface for your particular data communications application. It is assumed that you have set the hardware configuration switches (Chapter 3) as required. A select code value of 10 is assumed for all program statements shown. BASIC and HPL program statements are provided.<sup>1</sup> The appropriate I/O ROM(s) must be installed in your Desktop Computer.

### Setting Control or Data Mode

Since the same interface register (R4) is used for transfer of USART control and status information as well as data, some method of determining "which is which" must be provided. Bit 0 of the R5OUT register is used for this purpose.

When bit 0 of R5OUT is 0, all data transferred to the R4OUT register from the computer is sent over the data communications link by the USART as serial data and all data entered into the computer from the R4IN register is the serial data received by the USART from the data communications link.

When bit 0 of R5OUT is 1, the data transferred to the R4OUT register by the computer is interpreted as either the USART's mode or control word, and the data entered from the R4IN register into the computer is the USART status word.

---

#### NOTE

When you set bit 0 of R5OUT, you are then in the USART control or status mode. You must clear bit 0 of R5OUT before you can resume data transfers.

---

<sup>1</sup> The program lines shown must be modified for System 45A or 9825A Systems Programming ROM applications. See Appendix A.

## 30 Talking to the Interface

Here's the R5OUT register.

| Most Significant Bit             |              |                                  |              |             |                                               |                                                  |                                                           | Least Significant Bit |

|----------------------------------|--------------|----------------------------------|--------------|-------------|-----------------------------------------------|--------------------------------------------------|-----------------------------------------------------------|-----------------------|

| BIT 7                            | BIT 6        | BIT 5                            | BIT 4        | BIT 3       | BIT 2                                         | BIT 1                                            | BIT 0                                                     |                       |

| Interface<br>Interrupt<br>Enable | —            | Programmed<br>Interface<br>Reset | —            | —           | Interrupt<br>Control 2<br>Receiver<br>Control | Interrupt<br>Control 1<br>Transmitter<br>Control | R4 Control<br>0 = Data IN<br>OUT<br>1 = Control<br>Status |                       |

| BIT VALUE=128                    | BIT VALUE=64 | BIT VALUE=32                     | BIT VALUE=16 | BIT VALUE=8 | BIT VALUE=4                                   | BIT VALUE=2                                      | BIT VALUE=1                                               |                       |

Here's how to change bit 0 of R5OUT.

The following lines show how to set R5OUT to either control or data mode<sup>1</sup>

### BASIC

```

10  WAIT WRITE 10,5;1      0: wtc 10,1      ! Set R5OUT to CONTROL mode

20  WAIT WRITE 10,5;0      1: wtc 10,0      ! Set R5OUT to DATA mode

```

### Status

One important requirement of an interface is to provide you with status information. The 98036A interface returns two types of status information:

- Interface status.

- USART status.

### Interface Status

The status of the interface is contained in the R5IN register. Here's how to read the interface status from the R5IN register.

The following program lines read the interface status register (R5IN)<sup>1</sup>

### BASIC

### HPL

```

10  STATUS <10>;A      0: rds(10)>A      ! Get interface status

20  DISP "STATUS=";A      1: dsp"STATUS=",A  ! Display the Status value

STATUS= 272

```

<sup>1</sup> The program lines shown must be modified for System 45A or 9825A Systems Programming ROM applications. See Appendix A.

Here is the R5IN register.

| Most Significant Bit |                                   |              |                           |                           |             |             |                                |                                   | Least Significant Bit |  |

|----------------------|-----------------------------------|--------------|---------------------------|---------------------------|-------------|-------------|--------------------------------|-----------------------------------|-----------------------|--|

| BIT 8                | BIT 7                             | BIT 6        | BIT 5                     | BIT 4                     | BIT 3       | BIT 2       | BIT 1                          | BIT 0                             |                       |  |

| Peripheral Status 1  | Interface Interrupt Enable Status | 0            | Interface I.D. 0 Always 0 | Interface I.D. 1 Always 1 | 0           | 0           | Control Status 2 Receiver Mode | Control Status 1 Transmitter Mode |                       |  |

| BIT VALUE=256        | BIT VALUE=128                     | BIT VALUE=64 | BIT VALUE=32              | BIT VALUE=16              | BIT VALUE=8 | BIT VALUE=4 | BIT VALUE=2                    | BIT VALUE=1                       |                       |  |

The value returned into variable A is the summed total of the bit value(s) of all bits that are set (1). In the above example the status value is 272. This value means that bits 4 and 8 are set (16+256=272), and all other bits (0 through 3 and 5 through 7) are 0.

## USART Status

In order to obtain the status of the USART, you must first set bit 0 of R5OUT to the control mode (1), then perform an R4IN operation to return the USART status word.

The following program sets R5OUT to the control mode, reads the USART status register into variable "A", displays the USART status value, and sets R5OUT back to the data mode.<sup>1</sup>

|                                                                                                 |                                                                                                                                                                                                             |

|-------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BASIC                                                                                           | HPL                                                                                                                                                                                                         |

| <pre> 10  WAIT WRITE 10,5;1 20  A=READBIN(10) 30  DISP "STATUS=";A 40  WAIT WRITE 10,5;0 </pre> | <pre> 0: wtc 10,1           ! Set R5OUT to control mode 1: rdb(10)+A          ! Read USART Status register 2: dsp "STATUS=",A    ! Display the status 3: wtc 10,0           ! Set R5OUT to data mode </pre> |

STATUS= 5

Here is the USART status word.

| Most Significant Bit              |              |               |               |              |                   |                |                   |  | Least Significant Bit |  |

|-----------------------------------|--------------|---------------|---------------|--------------|-------------------|----------------|-------------------|--|-----------------------|--|

| BIT 7                             | BIT 6        | BIT 5         | BIT 4         | BIT 3        | BIT 2             | BIT 1          | BIT 0             |  |                       |  |

| Request To Send Pin 4(Standard)   |              |               |               |              |                   |                |                   |  |                       |  |

| Data Set Ready Pin 6 (Option 001) | Always 0     | Framing Error | Overrun Error | Parity Error | Transmitter Empty | Receiver Ready | Transmitter Ready |  |                       |  |

| BIT VALUE=128                     | BIT VALUE=64 | BIT VALUE=32  | BIT VALUE=16  | BIT VALUE=8  | BIT VALUE=4       | BIT VALUE=2    | BIT VALUE=1       |  |                       |  |

<sup>1</sup> The program lines shown must be modified for System 45A or 9825A Systems Programming ROM applications. See Appendix A.

The value returned into variable A is the summed total of the bit value(s) of all bits that are set (1). In this example the value of A is 5. This value means that bits 0 and 2 are set ( $1+4=5$ ), and all other bits (1, and 3 through 7) are 0.

## Resets

Three programmed resets are provided by the 98036A interface. The resets provided are:

- Programmed interface reset.

- Error bit reset.

- USART reset.

### Programmed Interface Reset

When the programmed interface reset is executed, the 98036A interface is reset to the power up default condition. The power up default conditions are:

- The USART mode word is reset to the default condition specified by the mode word switches.

- The USART control word is set to a decimal value of 5 (Bits 0 and 2 are 1).

- All other interface registers are cleared (set to 0).

In order to reset the interface, simply send a control word to set bit 5 of the R5OUT register. Here's the R5OUT register.

| R5OUT Register Bit Definitions |              |                            |              |                       |                                      |                                         |                                                      |

|--------------------------------|--------------|----------------------------|--------------|-----------------------|--------------------------------------|-----------------------------------------|------------------------------------------------------|

| Most Significant Bit           |              |                            |              | Least Significant Bit |                                      |                                         |                                                      |

| BIT 7                          | BIT 6        | BIT 5                      | BIT 4        | BIT 3                 | BIT 2                                | BIT 1                                   | BIT 0                                                |

| Interface Interrupt Enable     | —            | Programmed Interface Reset | —            | —                     | Interrupt Control 2 Receiver Control | Interrupt Control 1 Transmitter Control | R4 Control<br>0 = Data IN: OUT<br>1 = Control Status |

| BIT VALUE=128                  | BIT VALUE=64 | BIT VALUE=32               | BIT VALUE=16 | BIT VALUE=8           | BIT VALUE=4                          | BIT VALUE=2                             | BIT VALUE=1                                          |

Here's a program line to set bit 5 of R5OUT.

The following program line executes a PROGRAMMED INTERFACE RESET. R5OUT is automatically set to the data mode when this is executed.<sup>1</sup>

|                        |              |                     |

|------------------------|--------------|---------------------|

| BASIC                  | HPL          | C                   |

| 10 WAIT WRITE: 10,5;32 | 0: wtc 10,32 | ! Execute the RESET |

<sup>1</sup> The program lines shown must be modified for System 45A or 9825A Systems Programming ROM applications. See Appendix A.

## Error Bit Reset

When an error is detected in the received data, the USART sets an error bit in the USART status word. If you suspect that errors may exist in your input data you can periodically check the USART status word (see USART Status) for the presence of error bits. If errors have been detected you should reset the error bits in order to detect any subsequent errors.

To reset the USART error bits you must first set bit 0 of R5OUT to the control mode (1), then perform an R4OUT operation with bit 4 set.

Here's the USART control word.

| USART Control Word   |              |                                                                     |                                        |                       |                      |                                                                           |                         |

|----------------------|--------------|---------------------------------------------------------------------|----------------------------------------|-----------------------|----------------------|---------------------------------------------------------------------------|-------------------------|

| Most Significant Bit |              |                                                                     |                                        | Least Significant Bit |                      |                                                                           |                         |

| BIT 7                | BIT 6        | BIT 5                                                               | BIT 4                                  | BIT 3                 | BIT 2                | BIT 1                                                                     | BIT 0                   |

| Always 0             | USART Reset  | Clear To Send Pin 5(Standard)<br>Request To Send Pin 4 (Option 001) | Reset Status Bits of USART Status Word | Send Break Character  | Enable Data Receiver | Data Set Ready Pin 6(Standard)<br>Data Terminal Ready Pin 20 (Option 001) | Enable Data Transmitter |

| BIT VALUE=128        | BIT VALUE=64 | BIT VALUE=32                                                        | BIT VALUE=16                           | BIT VALUE=8           | BIT VALUE=4          | BIT VALUE=2                                                               | BIT VALUE=1             |

Here's how to reset the USART error bits.

The following program lines set R5OUT to the control mode, resets the USART error bits, and sets R5OUT back to the data mode.<sup>1</sup>

BASIC

HPL

|                      |              |                              |

|----------------------|--------------|------------------------------|

| 10 WAIT WRITE 10,5;1 | 0: wtc 10,1  | ! Set R5OUT to control mode  |

| 20 WRITE BIN 10;16   | 1: wtb 10,16 | ! Reset the USART error bits |

| 30 WAIT WRITE 10,5;0 | 2: wtc 10,0  | ! Set R5OUT to data mode     |

## USART Reset

When a USART reset is executed, the USART is forced into an idle mode.<sup>2</sup> The next data byte sent to the interface must be a new mode word for the USART. The USART then begins operating in the mode specified by the new mode word (see "USART Mode Word," page 34). The USART reset does NOT reset the interface but does reset the error bits. In order to reset the USART you must first set bit 0 of R5OUT to the control mode (1), then perform an R4OUT operation with bit 6 set.

<sup>1</sup> The program lines shown must be modified for System 45A or 9825A Systems Programming ROM applications. See Appendix A.

<sup>2</sup> Because the USART is forced into the idle mode, data may be lost if it has not been completely transmitted. To avoid this potential loss, 2 null (0) or del (255) characters should be sent before resetting the USART.

Here's the USART control word.

| Most Significant Bit |             |                                                                     |                                        |                      |                      |                                                                           |                         | Least Significant Bit |              |              |              |             |             |             |             |

|----------------------|-------------|---------------------------------------------------------------------|----------------------------------------|----------------------|----------------------|---------------------------------------------------------------------------|-------------------------|-----------------------|--------------|--------------|--------------|-------------|-------------|-------------|-------------|

| BIT 7                | BIT 6       | BIT 5                                                               | BIT 4                                  | BIT 3                | BIT 2                | BIT 1                                                                     | BIT 0                   | BIT 7                 | BIT 6        | BIT 5        | BIT 4        | BIT 3       | BIT 2       | BIT 1       | BIT 0       |

| Always 0             | USART Reset | Clear To Send Pin 5(Standard)<br>Request To Send Pin 4 (Option 001) | Reset Status Bits of USART Status Word | Send Break Character | Enable Data Receiver | Data Set Ready Pin 6(Standard)<br>Data Terminal Ready Pin 20 (Option 001) | Enable Data Transmitter | BIT VALUE=128         | BIT VALUE=64 | BIT VALUE=32 | BIT VALUE=16 | BIT VALUE=8 | BIT VALUE=4 | BIT VALUE=2 | BIT VALUE=1 |

Here's how to reset the USART.

The following program lines set R50UT to control mode and reset the USART. The USART then interprets the next data byte from the Desktop Computer as a new USART mode word.<sup>1</sup>

|                      |                                         |

|----------------------|-----------------------------------------|

| BASIC                | HPL                                     |

| 10 WAIT WRITE 10,5;1 | 0: wtc 10,1 ! Set R50UT to control mode |

| 20 WRITE BIN 10;64   | 1: wtb 10,64 ! Reset the USART          |

The next write operation to the interface MUST be a new USART mode word. The USART mode word is explained next.

## USART Mode Word

When the USART reset has been executed (see USART reset, page 33) the USART clears the previous mode word, goes into an idle state, and waits for the computer to send a new mode word. A new mode word can NOT be sent to the USART unless a USART reset (setting bit 6 of USART Control word) has been executed.

Here's the USART mode word.

| Most Significant Bit                                                        |                                |                                        |                                                                      |                                                                                                           |               |              |              | Least Significant Bit |             |             |             |             |       |       |       |

|-----------------------------------------------------------------------------|--------------------------------|----------------------------------------|----------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|---------------|--------------|--------------|-----------------------|-------------|-------------|-------------|-------------|-------|-------|-------|

| BIT 7                                                                       | BIT 6                          | BIT 5                                  | BIT 4                                                                | BIT 3                                                                                                     | BIT 2         | BIT 1        | BIT 0        | BIT 7                 | BIT 6       | BIT 5       | BIT 4       | BIT 3       | BIT 2 | BIT 1 | BIT 0 |