# **HP 95LX Developer's Guide**

**Copyright Hewlett-Packard Company 1991

All rights reserved**

**1st Revision

August 30, 1991**

---

## Notice

This manual and the software described herein are provided "as is" and are subject to change without notice. Hewlett-Packard Company makes no warranty of any kind with regard to this manual or the software described herein, including, but not limited to, the implied merchantability and fitness for a particular purpose. Hewlett-Packard Co. shall not be liable for any errors or for incidental or consequential damages in connection with the furnishing, performance, or use of this manual or the software described herein.

Copyright Hewlett-Packard Co. 1991. All rights reserved. Reproduction, adaptation, or translation of this manual, including any programs, is prohibited without prior written permission of Hewlett-Packard Company, except as allowed under copyright laws.

Corvallis Division

1000 NE Circle Blvd.

Corvallis, OR 97330, U.S.A.

---

## Printing History

|                   |                 |

|-------------------|-----------------|

| Preliminary Draft | May 1, 1991     |

| 1st Revision      | August 30, 1991 |

## **Important Note to Software Developers**

Hewlett-Packard is committed to making your current and future development efforts as easy as possible. In keeping with this commitment, Hewlett-Packard recommends that developers avoid using HP 95LX hardware specific features for I/O. Software written using HP 95LX hardware specific features is very likely not to run on future HP product.

## HP 95LX Technical Information

### **Table of Contents:**

|                                                            | <b>Pages</b> |

|------------------------------------------------------------|--------------|

| 1. ISV Developer's Overview                                | 1-1 to 1-4   |

| 2. Off-the-Shelf Development Tools                         | 2-1          |

| 3. HP 95LX DOS                                             | 3-1          |

| 4. HP 95LX BIOS ERS                                        | 1 to 104     |

| 5. File Specifications for HP 95LX Built-in Applications   | 4-1 to 4-9   |

| 6. HP 95LX Memory Management                               | 6-1 to 6-2   |

| 7. HP 95LX Low-Level Graphics Support                      | 7-1 to 7-21  |

| 8. HP 95LX System Manager Operation and Programmer's Guide | 7-1 to 7-18  |

| 9. HP 95LX System Manager Services Reference               | 8-1 to 8-60  |

| 10. From Software Design to Ordering ROM Cards             | 10-1 to 10-7 |

| 11. 'Hopper' HP 95LX System Controller ERS                 | 1 to 80      |

| 12. HP 95LX Wired Serial and Infrared I/O ERS              | 1 to 15      |

| 13. Custom Artwork                                         | 14-1         |

| 14. PC Card Standard (PCMCIA 1.0)                          | 1 to 102     |

## ISV Developer's Overview

---

The information contained in this notebook is intended for Independent Software Vendor (ISV) use in planning of software development or adaptation tasks. It is hoped that this information will provide you with enough details about the Jaguar platform in order to formulate a strategy for adapting your product to the HP 95LX.

---

### Levels of Adaptation

Most programs intended to run on The HP 95LX will require or at least benefit from being modified to conform to The HP 95LX hardware. Assuming that this has been considered, the next consideration is how the software will run on The HP 95LX. The The HP 95LX platform provides three options in this area:

1. Run from RAM as an independent DOS program. Such a program would be compiled and linked with standard DOS tools and would be loaded and executed by DOS exactly as on a standard PC.

There are several distribution options for these programs. All that is required for execution is that they reside on a The HP 95LX disk. Hence they could be down loaded to The HP 95LX's internal disk from a PC or a modem connection, or they could be distributed on a plug-in ROM card which has been formatted as a disk.

This is the simplest execution option. However it may be the least RAM efficient and it will not be integrated with The HP 95LX's built-in applications.

2. Run as an independent ROM executable XIP (eXecute In Place) program. Such a program would be distributed on a ROM card and at execution time would bank switch its code into the CPU address space using The HP 95LX's bank switching capabilities.

The advantage of this over option 1 is greater RAM efficiency. There is still no integration with the built-in applications.

This level of adaptation will require the code to be ROMable, will require the use of special software tools to prepare the ROM image and will require the program to use The HP 95LX's bank switching services. The necessary tools and services are not completely described in this document, but will be defined in the developer's kit. See the "Memory Management" chapter for more information on XIP.

3. Run under the System Manager. Such a program will be called System-Manager-compliant and can be either RAM executable or XIP.

Under this option, the program has access to the same set of services that are used by the built-in applications. For example, this enables the program to share a non-preemptive multitasking environment with the built-in applications so that the user can conveniently switch between tasks.

The "System Manager Guide" and "System Manager Reference" sections deal with writing System-Manager-compliant applications.

---

## **The HP 95LX Hardware Overview**

The HP 95LX is a Palmtop PC which is very PC compatible except in areas which have been customized to obtain its small size or to support large amounts of memory. These areas are highlighted here.

### **Display**

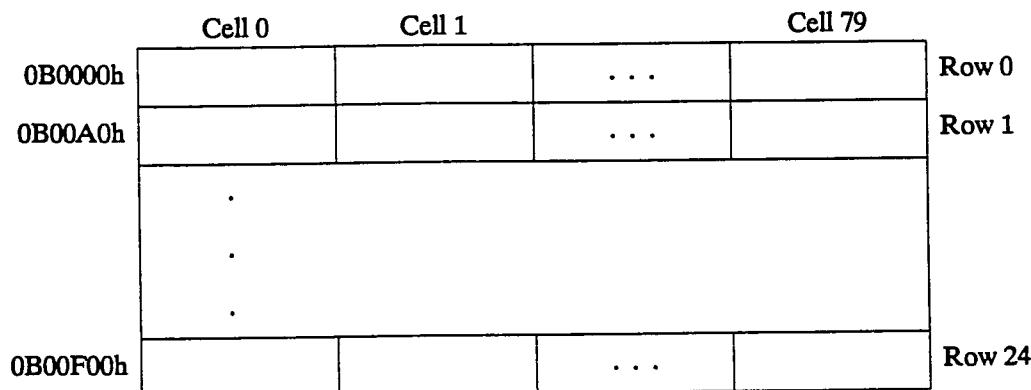

The HP 95LX's physical display is 40 characters by 16 lines in text mode. This display is a window into an MDA standard 80 character by 25 line display RAM. While there is provision for windowing the physical display around the larger display RAM, it is expected that most software development for The HP 95LX will include customization to a 40 by 16 screen.

The HP 95LX's display also has a (non-standard) graphics mode which has pixel dimensions of 240 columns by 128 rows.

### **Character Font**

The HP 95LX character fonts are stored in ROM. Codepage 850 was used since it contains international characters. This was chosen to facilitate the localization of the product. Developers should be aware that the standard for PC's is codepage 437 which contains line drawing characters.

### **Keyboard**

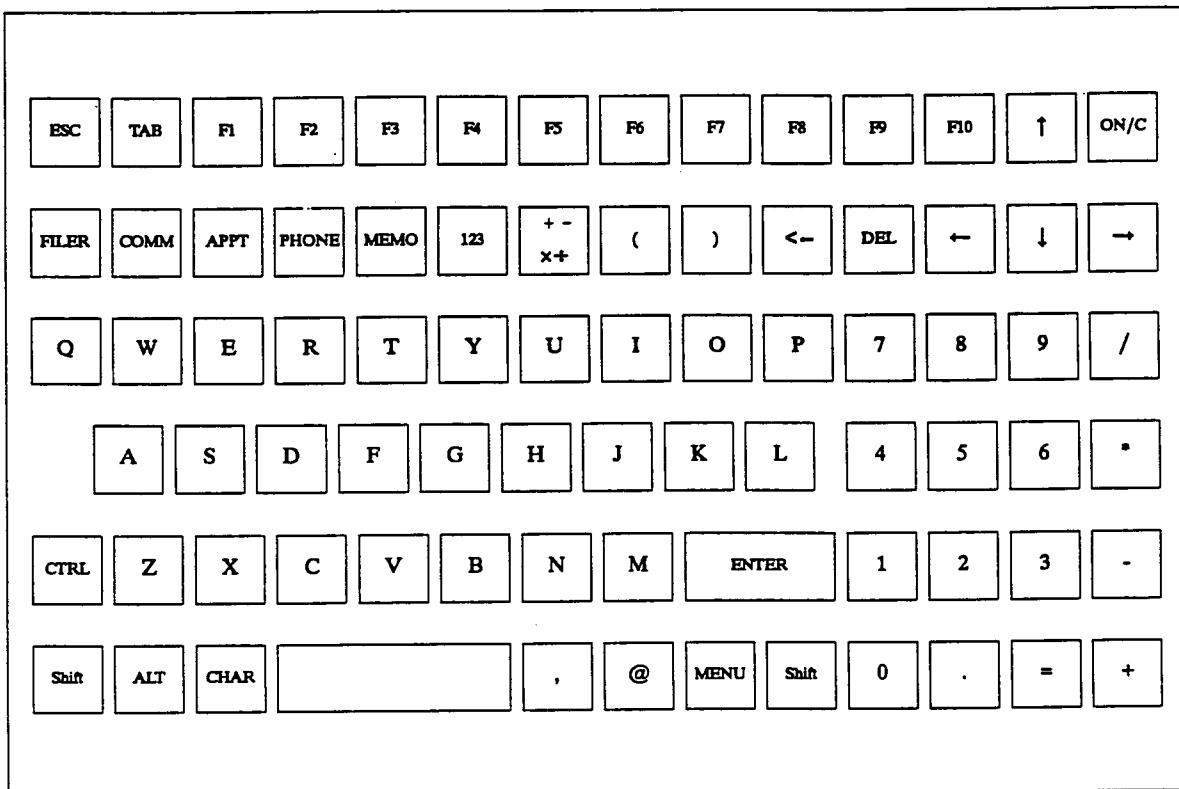

The HP 95LX's keyboard is shown in figure 1. See the BIOS Int 9h documentation for the scan/ASCII codes corresponding to each key.

### **Memory Structure**

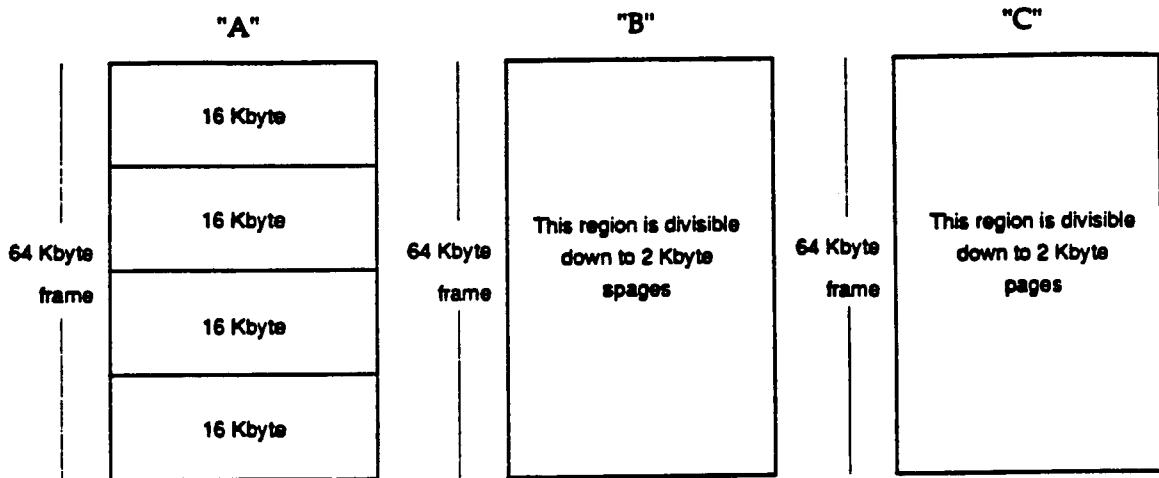

The HP 95LX has more "logical" memory (i.e., memory residing on memory chips) than can be accommodated in the 1 megabyte "physical" address space of the CPU. Bank switching is used to access the additional memory. For example, Figure 2 shows that bank switching is used to access the code for the built-in applications and to access the memory on a plug-in card. See the "Memory Management" chapter for more information.

### **Plug-in Cards**

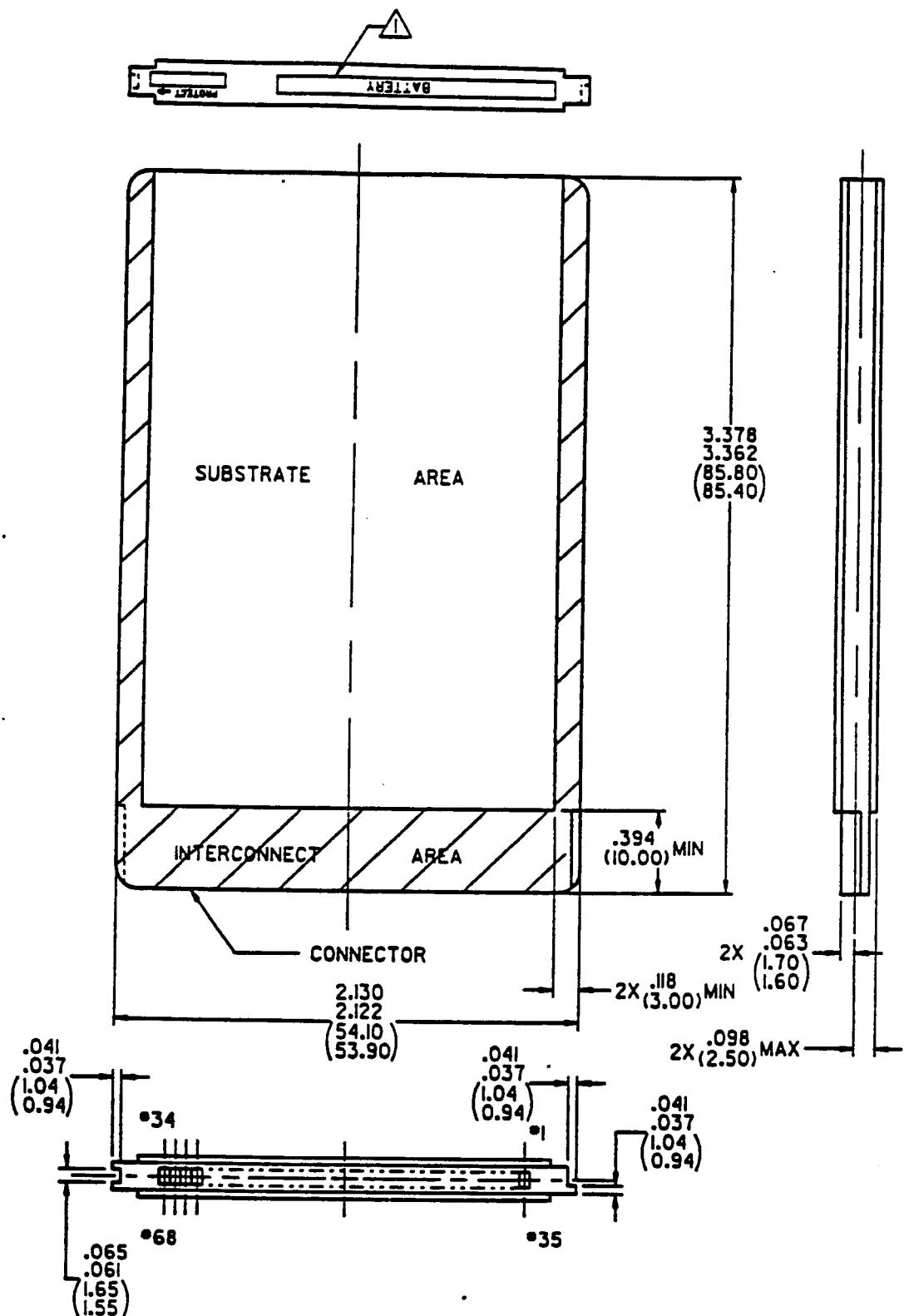

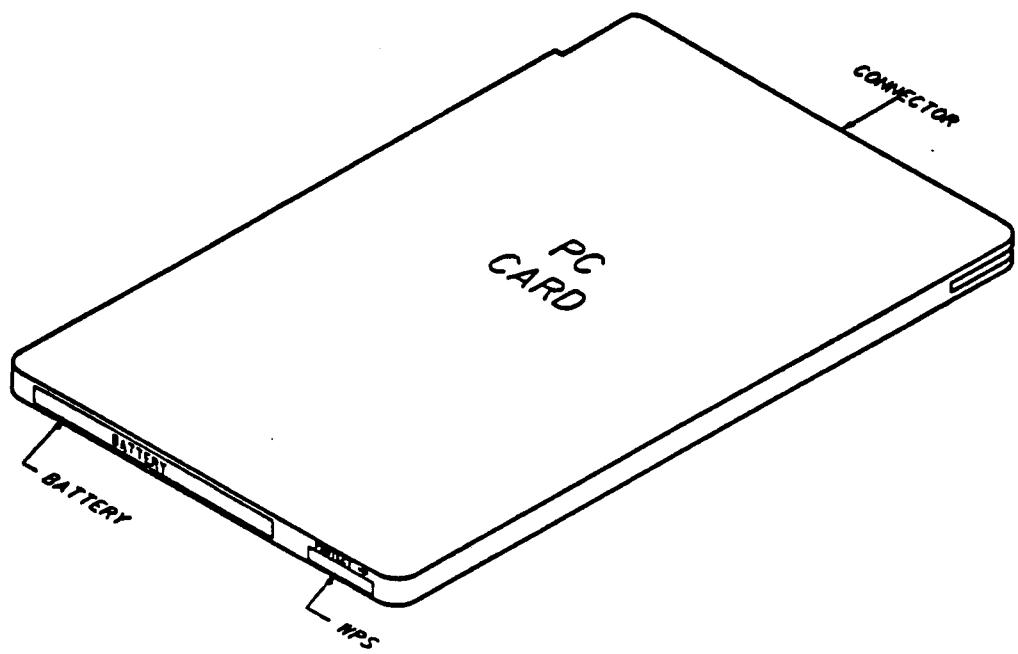

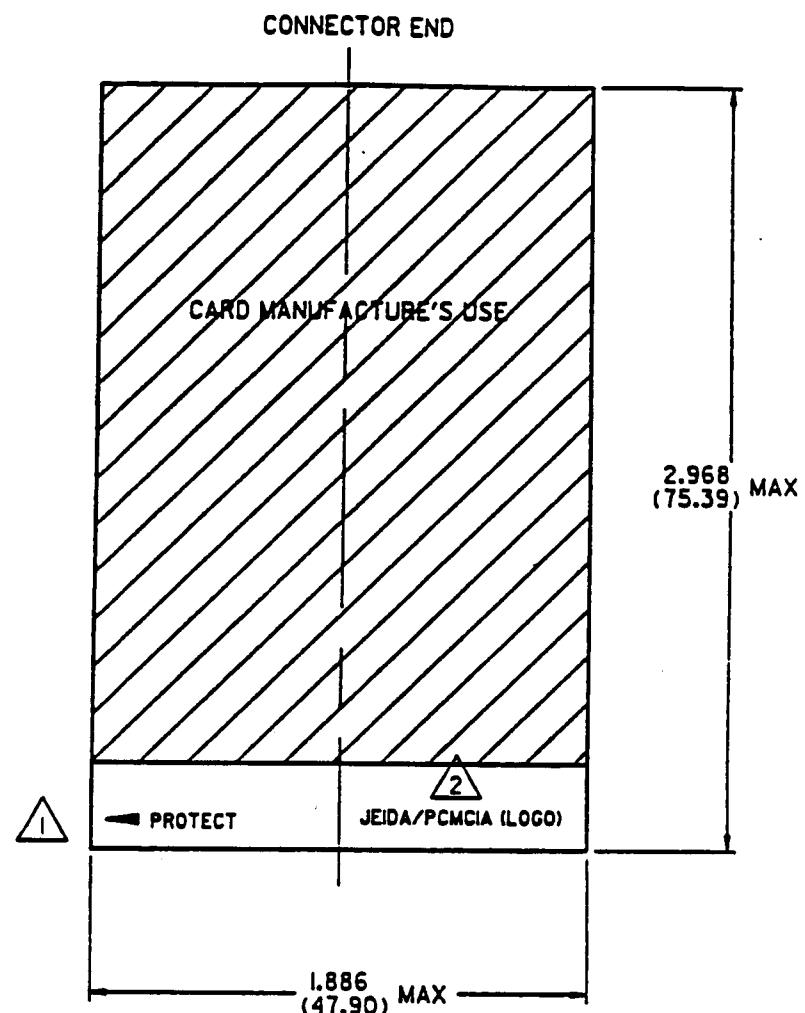

The HP 95LX has one plug-in card slot which accommodates a PCMCIA/JEIDA standard memory card. This card slot is somewhat analogous to a floppy disk drive on a standard PC. There are two main types of cards.

One is a battery-backed RAM card which is formatted as a RAM disk. This type of card is analogous to a floppy disk. RAM cards will be available in 128K and 512K byte sizes.

The other is a ROM card which contains application software. This card could be formatted as a disk in which case it would be analogous to a read-only disk. A ROM card can also

contain XIP software designed to be bank switched into CPU address space rather than accessed as a disk file. ROM cards will be available 1 and 2 megabyte sizes.

---

## The HP 95LX Software Overview

### Built-in Applications

The HP 95LX features eight built-in applications: Lotus 1-2-3, HP calculator, Memo, Phone Book, Appointment Book, Terminal Emulator, Filer, and Setup. These applications are accessed by pressing their corresponding key, see figure 1.

### System Manager

The System Manager is the control program which runs the built-in and other System-Manager-compliant applications.

All the built-in applications execute from ROM under the direction of the System Manager. Briefly, when an application's key is pressed, the System Manager deactivates any current application, performs any necessary bank switching to access the code for the requested application and starts up the new application. This is termed non-preemptive multitasking since that application being deactivated gets a chance to "clean up" before losing control.

See "System Manager Guide" and "System Manager Reference" for more information.

### DOS

The HP 95LX uses Microsoft DOS 3.22. This version of DOS was chosen because it executes from ROM leaving the maximum amount of RAM available for applications.

The DOS kernel functions are always available and provide access to the DOS command processor. However, since the emphasis of The HP 95LX is on applications, The HP 95LX does not contain the full set of DOS external commands. See the "DOS" chapter for notes on how DOS has been customized for The HP 95LX.

### BIOS

The HP 95LX contains a ROM BIOS layer which provides the standard interface as well as many extensions to support The HP 95LX specific hardware. See the "BIOS" chapter for details.

### Disks

The HP 95LX's disk support is patterned after that of a PC which has an internal hard disk drive and one floppy disk drive.

The HP 95LX's internal disk, which is named C:, is a combination RAM/ROM disk. The ROM disk portion contains a variety of files such as help files for the built-in applications and utility programs such as FORMAT. The RAM disk portion contains user files and resides in system RAM. The size of the RAM disk is user settable using the "Setup" application.

The HP 95LX uses plug-in battery-backed RAM cards formatted as RAM disks for its "floppy" disks. The plug-in port is the A: (or B:) drive, analogous to a single floppy drive on a PC.

## Off-the-Shelf Development Tools

---

Since the HP 95LX runs Microsoft DOS version 3.22, compilers, assemblers, and debuggers compatible with this version of DOS can be used to develop software for the HP 95LX. Some development packages such as Turbo-C from Borland support remote debugging over a serial interface. This configuration works on the HP 95LX and is very useful for certain types of software development.

Since the HP 95LX is a relatively small PC, users of off-the-shelf tools should make certain they understand what overhead is built into the *use* of their tools. Two examples follow:

- Run time support libraries sometimes include modules that are not needed by the main program.

- Users building HP 95LX system-manager-compliant programs need to be aware of any library initialization code their package automatically includes in programs they build. Much of this sort of initialization code is incompatible with the HP 95LX System Manager. Steps can usually be taken to use library routines that do not require initialization.

## HP 95LX DOS

---

### Introduction

The HP 95LX contains the primary components of ROM-executable MS-DOS 3.22.

More specifically, the HP 95LX contains the DOS Kernel and the command processor, but only a few external commands.

Generally speaking, DOS works the same on the HP 95LX as it would on a standard PC (except for the missing external commands). For this reason, these notes discuss only the *differences* between the operation of MS-DOS 3.22 on the HP 95LX and DOS's operation on a standard PC.

### DOS Boot Sequence

On a standard PC, DOS boots off disk and runs from RAM. On the HP 95LX, DOS boots out of ROM and runs from ROM. Thus on the HP 95LX DOS, RAM requirements are greatly reduced since only DOS data is stored in RAM.

There is no provision on the HP 95LX to boot from disk. However, a disk can contain CONFIG.SYS and AUTOEXEC.BAT files—see below.

### DOS Initialization

On a standard PC, DOS makes the boot disk drive the default drive and searches the root directory of that drive for a CONFIG.SYS file.

On the HP 95LX, DOS initialization has been changed to first search for CONFIG.SYS on the A: drive and, if not found, to search on the C: drive. If CONFIG.SYS is found on the A: drive, then that CONFIG.SYS is processed and A: is made the default drive. In this case, any CONFIG.SYS that is on the C: drive will not be processed. If CONFIG.SYS is not found on the A: drive, then C: is made the default drive and any CONFIG.SYS found there will be processed.

### The DOS EXEC Function

In ROM-executable MS-DOS 3.22, the EXEC function has been extended to first search a table of ROM-executable programs before searching disk in case the program name has no drive path specified.

On the HP95LX, the table contains the two names COMMAND and \$SYSMGR. The COMMAND program is the DOS command processor and the \$SYSMGR program is the System Manager.

## **The Default Shell**

On standard DOS systems, the default shell is COMMAND.COM. On the HP 95LX, COMMAND.COM is the System Manager.

The System Manager is the program that directs execution of the built-in and special add-on applications. The HP 95LX System Manager does not process any AUTOEXEC.BAT files.

## **The DOS Command Processor**

COMMAND.COM is available in the HP 95LX, but is not normally run at initialization time since DOS goes directly to the System Manager shell. There are two ways to access the command processor:

1. Invoke the command processor from within the System Manager program.

2. Change the shell to the command processor by including the line

**SHELL=COMMAND /P**

in the CONFIG.SYS file and reboot.

This causes DOS to go directly to COMMAND.COM — the System Manager is not invoked and the built-in application keys will not be active. The commands that are available are the internal command processor commands, any external programs on disk, and the two ROMed program commands listed above.

One use of this method is to get access to DOS in order to perform some custom initialization and then run the System Manager using the \$SYSMGR command.

## **Disk-Resident External Commands**

The HP 95LX contains two external commands, COMMAND.COM and CHKDSK.EXE, which reside in the root directory of the ROM disk.

The COMMAND.COM program is only a stub that invokes the actual command processor residing in ROM. This stub is provided in case some program accesses the command processor by its full name (including extension). As mentioned above, COMMAND (without path or extension) will be executed directly from ROM.

CHKDSK is the standard DOS check disk command.

The HP 95LX also contains DEBUG.EXE in a hidden directory called \_SYS. This directory is off the root of the ROM disk. This is the standard DOD DEBUG program.

## **International Support**

MS-DOS 3.22 supports the COUNTRY= configuration parameter and DOS calls that allow tailoring DOS and applications to local language characteristics. Some of this information depends on the the PC's character set. DOS 3.22 supports only code page 437 (switchable code pages start with DOS 3.3). Since the HP 95LX uses code page 850, the country-specific information in HP 95LX DOS has been updated to match code page 850.

Note however that the international support that is built into the System Manager does not use these DOS capabilities.

# **JAGUAR BIOS**

## **External Reference Specification**

**Version 2.02**

**May 1, 1991**

**Hewlett-Packard Company**

## Overview

This is the specification of the Jaguar ROM Basic Input/Output System (BIOS). The BIOS provides the lowest level of software support for applications running on Jaguar. This specification describes in detail the implementation of the Jaguar BIOS. The Jaguar BIOS is designed to be completely compatible with IBM's new version of the PC-XT. In addition to the PC-XT BIOS functions, the Jaguar BIOS includes a small number of BIOS functions which are compatible with the IBM-AT.

The Jaguar BIOS is based upon an XT level BIOS source code obtained from Phoenix Software Associates (PSA). The code HP purchased from PSA was written to be compatible with the IBM PC-XT of pre-April 1986 vintage, i.e. before the introduction of a new version of the XT with the enhanced keyboard. To our knowledge, the PSA XT code received by HP was written by Phoenix without infringing on any of IBM's copyrights to the XT BIOS code. In the same spirit, HP has added and modified the code without copyright infringement.

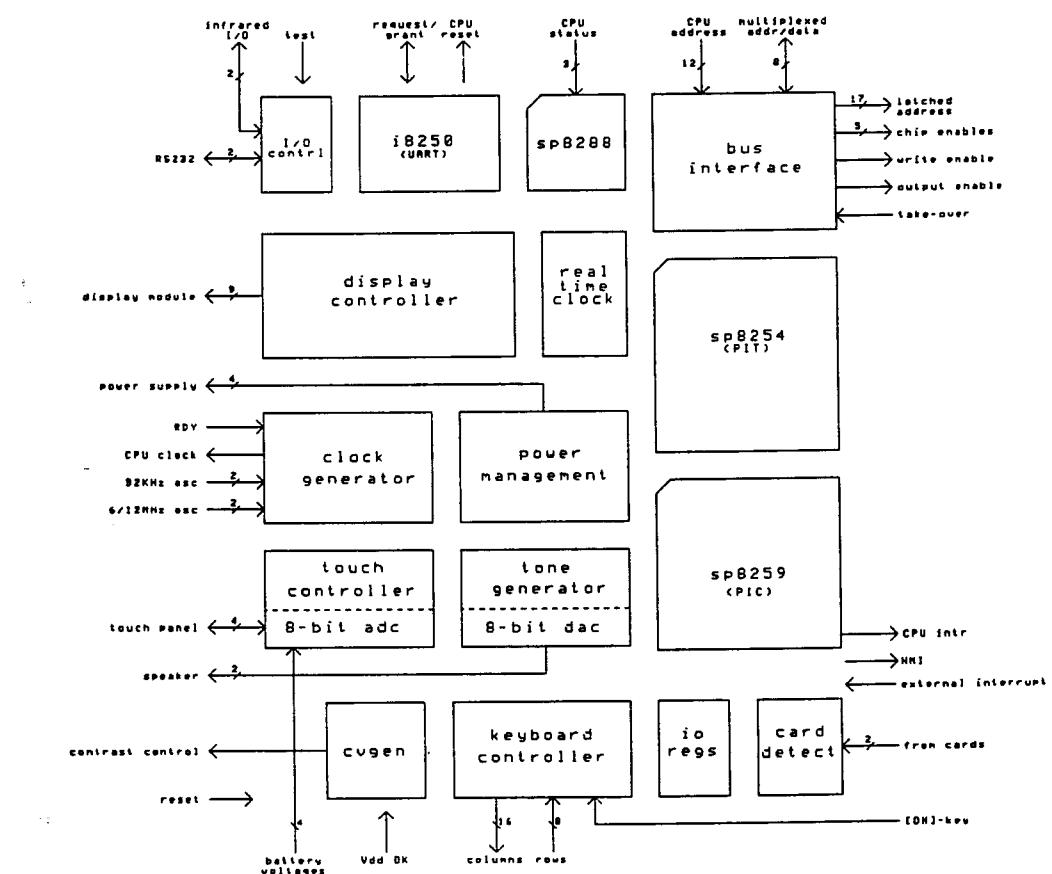

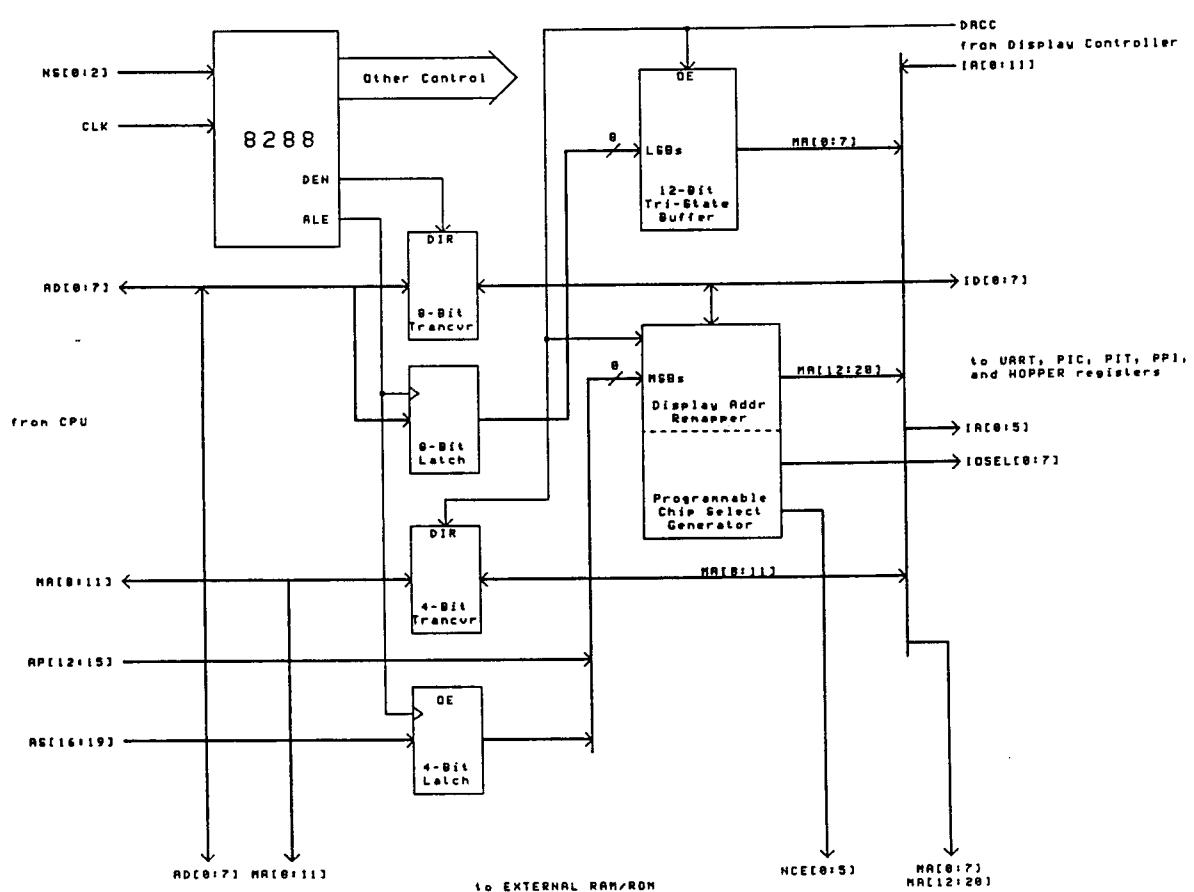

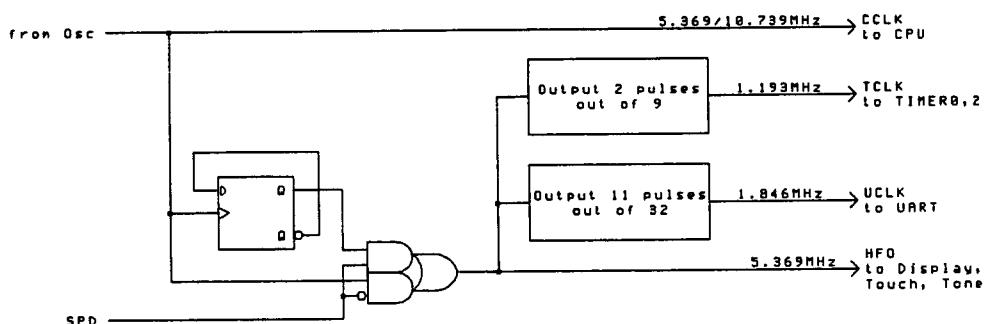

## Jaguar Hardware set

Jaguar is an Information Management Calculator. It features an 8088 processor and hardware set that is moderately compatible with an IBM-XT. Differences between Jaguar and XT hardware are listed below:

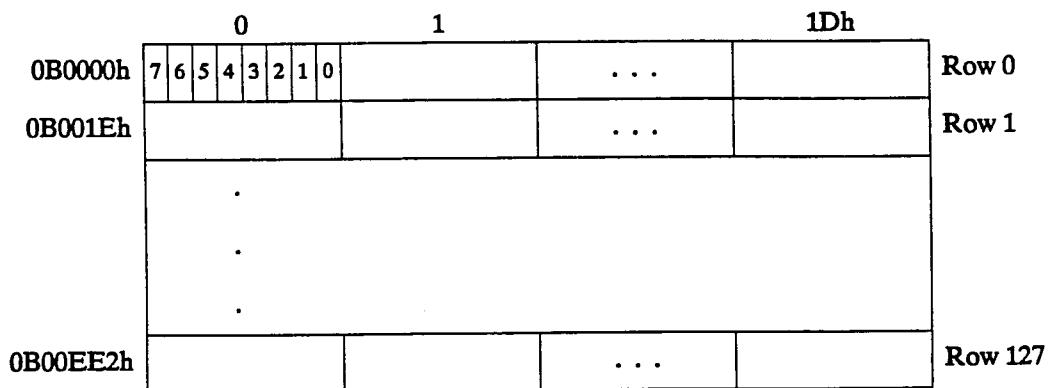

- Jaguar has a smaller display than a XT. The jaguar display size is 40 x 16 (text) or 240 x 128 dots (graphics) vs XT's monochrome display size of 80 x 25 (text) or 320 x 200 dots (CGA graphics). The Display RAM in Jaguar is the same size as that of an XT with a Monochrome Display Adapter(4K bytes). Also, there is provision to window around in the display RAM, so the user can see the contents of all 4K of RAM.

- Jaguar's display cursor size control is different from that of an IBM-XT.

- Jaguar has no mechanical disk. Instead there is a built-in RAM disk.

- Jaguar has a different keyboard layout from the IBM-XT.

- Jaguar's keyboard management is different from the IBM-XT. Keyboard Scans are implemented in software in Jaguar, while they are performed by an 8048 microcontroller in a XT. However, the Jaguar keyboard interrupt service routine will emulate the 8048.

- Jaguar supports plug-in ROMs.

- Jaguar supports plug-in RAMs. All memory in plug-in RAM will be used as RAM disk.

- Jaguar is switched ON or OFF under software control. This is compared to an XT which is switched ON or OFF by a hardware switch that controls power to the entire machine.

- Jaguar has LCD contrast adjustment under software control. This is fundamentally different from XT brightness control, which is done with a potentiometer adjustment.

- Jaguar does not support a parallel printer. However, it does support a serial printer which uses XON-XOFF flow control.

- Jaguar supports only one serial port UART. However the serial channel can be directed either to the IR or wired serial port.

- Jaguar RAM is 8 bits wide. There is no parity bit, as in the IBM-XT.

- Jaguar's hardware interrupt set is not identical in function to an XT.

## Changes to PSA Code

The following changes were made to the PSA code. This list is just touches on the major changes. To obtain more information on the changes made, refer to the chapter on the BIOS Interrupts or go straight to the BIOS source code.

|                |                                                                                                                                                                                                                                                                                                                              |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <Reset Vector> | Power On Code was changed so that turning the machine on causes the machine to return to the application that was running before the system was powered down.                                                                                                                                                                |

| Int 02         | Nonmaskable interrupt (NMI).<br>This is invoked in the IBM-XT when a RAM parity error occurs. It is invoked on Jaguar by either a Low Battery or Module Pulled event.                                                                                                                                                        |

| Int 05         | Print Screen Interrupt.<br>This prints the contents of the active display window only, not the contents of the entire display memory as in the IBM-XT.                                                                                                                                                                       |

| Int 06         | Low Power Hook<br>This interrupt is called by the system: <ul style="list-style-type: none"><li>– Just before going to light sleep.</li><li>– Just after awakening from light sleep.</li><li>– Just before going to deep sleep.</li><li>– Just after awakening from deep sleep.</li></ul>                                    |

| Int 08         | Timer hardware service.<br>The timer service was modified to add display window control and battery level checks.                                                                                                                                                                                                            |

| Int 09         | Keyboard interrupt.<br>Int 09 was modified to support Char key translations, Mute key translations and the ALT-NUMPAD code was modified to work with top row number keys instead of number pad keys.                                                                                                                         |

| Int 0A         | Miscellaneous interrupt.<br>This is a reserved interrupt in the IBM-XT.                                                                                                                                                                                                                                                      |

| Int 0B         | Keyboard and touch panel hardware interrupt.<br>In Jaguar, hardware keyboard interrupt in Jaguar is INT Bh, not INT 09. INT 0Bh code debounces pressed keys and places key code in the keycode register (I/O address 60h). Then it invokes the INT 09 service routine.<br>NOTE: INT 0Bh is the COM2 interrupt in the IBM-XT. |

| Int 0D         | HOPPER IR Interrupt<br>This is the fixed disk interrupt in the IBM-XT.                                                                                                                                                                                                                                                       |

| Int 0E         | External XINT pin hardware interrupt routine.<br>This is diskette interrupt in the IBM-XT.                                                                                                                                                                                                                                   |

| Int 0F         | HOPPER RTC interrupt.<br>This is the LPT1 interrupt in the IBM-XT.                                                                                                                                                                                                                                                           |

| Int 10         | Video Services<br>Changed CGA functions to maintain a moderate degree of compatibility.<br>Left MDA functions intact.                                                                                                                                                                                                        |

## Overview

Int 13            **Disk services.**

Modified to work with a RAM disk.

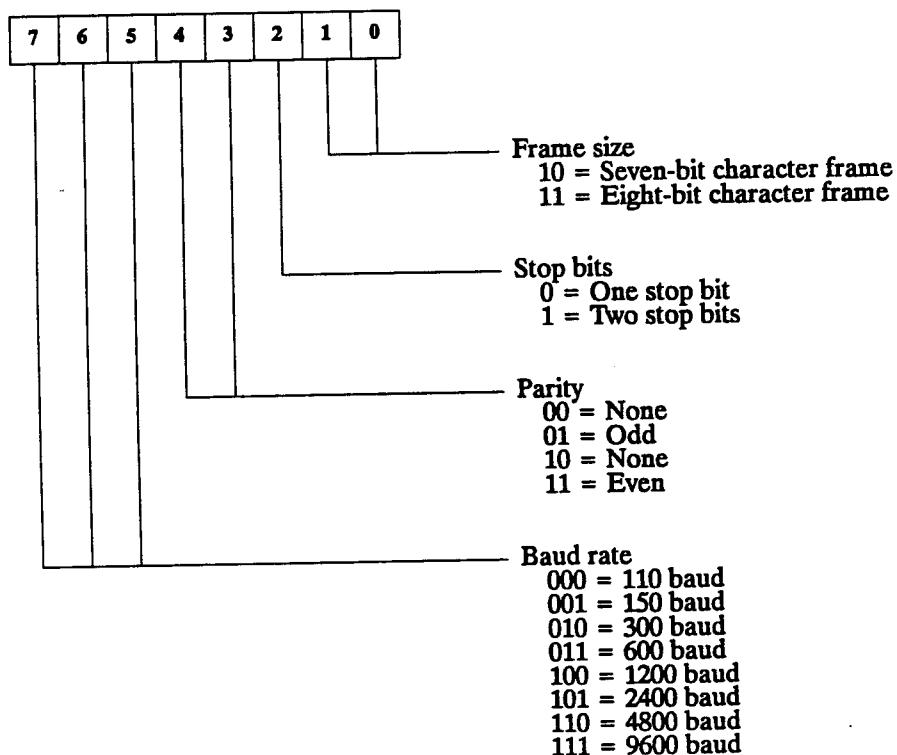

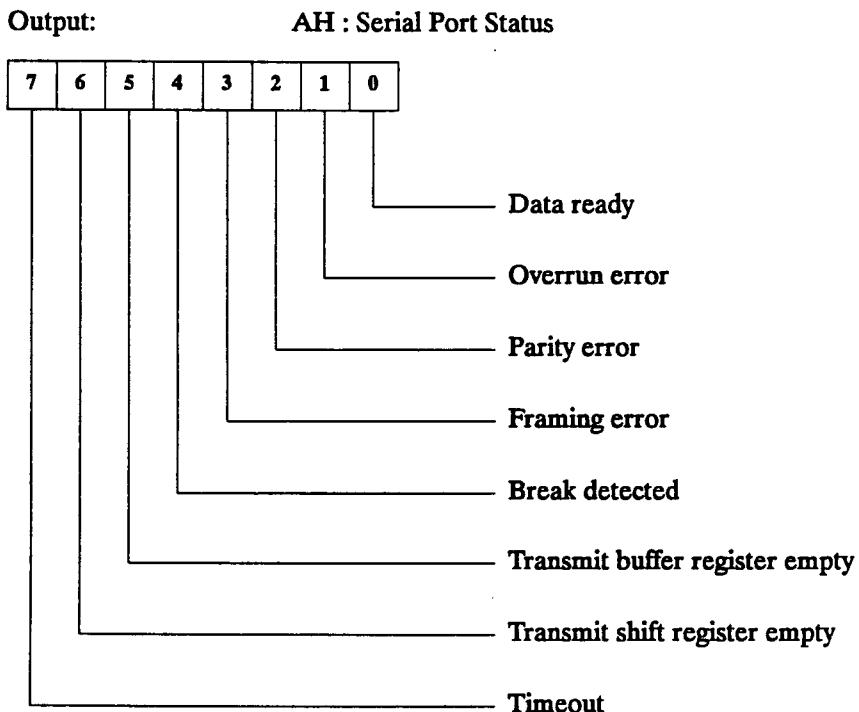

Int 14            **Serial Port Services.**

Removed waits for DSR and CTS set when sending a character. Removed wait for DSR set when receiving a character. The receive character service changes the serial port interrupt vector to point to a dummy interrupt service routine (just an IRET).

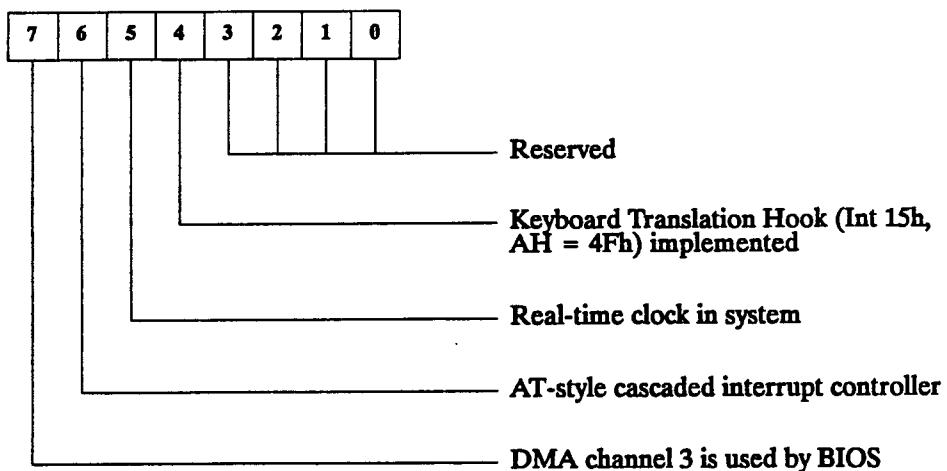

Int 15            **System services (Cassette control in now defunct XT)**

Just about all of Int 15 is new. Keyboard translation hook (Int 15 function 4F)

Int 16            **Keyboard Services.**

Modified to trap [ON] key press while machine is running. Also invokes light sleep code.

Int 17            **Printer services**

Modified to work with a serial printer. It implements the XON-XOFF handshake in Jaguar. These services change the serial port vector to point to a serial service routine that handles XON-XOFF handshakes.

Int 19            **Boot service**

Now boots DOS from ROM.

Int 1A            **Time of day services**

Added support of real time clock, including the capability of setting an alarm. The alarm is capable of turning on power to the unit.

Int 1E            Set to a dummy IRET.

This is the disk parameter table in the IBM-XT.

Int 1F            **Graphics character table pointer**

This points to a code page 850 font for characters 80h - FFh.

The following PSA interrupt handlers were not modified:

|        |                                                          |

|--------|----------------------------------------------------------|

| Int 11 | Equipment check service                                  |

| Int 12 | Get memory size service                                  |

| Int 14 | Serial port service                                      |

| Int 1B | Keyboard break default handler                           |

| Int 1C | Timer tick default handler (how can you change an IRET?) |

| Int 1D | Video parameter table                                    |

## BIOS RAM Definition

### BIOS RAM Definition

This chapter describes how memory is organized and used by the BIOS.

|                              |             |

|------------------------------|-------------|

| Interrupt Vectors            | 00000h      |

| BIOS Data Area               | 00400h      |

| DOS Data Area                | 00600h      |

| Memory Mapped Display RAM    | 001000h     |

| DOS Data Area                | 02000h      |

| Disk Operating System (DOS)  | (Variable)* |

| Application Program Area     | (Variable)* |

| RAM Disk Portion of Drive C: | (Variable)* |

| Unused                       | 80000h      |

| OS Functions                 | A0000h      |

| MDA RAM                      | B0000h      |

| Unused                       | B1000h      |

| Two 64KB Page Frames         | C0000h      |

| Four 16KB Page Frame         | E0000h      |

| BIOS ROM                     | F0000h      |

|                              | FFFFFh      |

\* Size of the Disk Operating System area varies since optional drivers and buffers may occupy variable amounts of RAM.

**Interrupt Vector Table.** The interrupt vector table is in the address range from 0:0000h through 0:3ffh. Vectors used by BIOS are initialized by the BIOS initialization code.

The table below lists the interrupt vector assignments and identifies each interrupt by function and type. The interrupts consist of four types: services, ISRs, hooks, and tables:

- A service is an application program callable interrupt. Such interrupts provide functions that an application can call by using the appropriate Int instruction.

- An ISR is a hardware interrupt service routine. These routines should not be called from applications since unpredictable results may occur.

- A hook is an interrupt service routine provided for applications to optionally take over.

- A table is a pointer to a table of data bytes.

| Int     | Address Range (Hex) | Function                                      | Type    |

|---------|---------------------|-----------------------------------------------|---------|

| 00h     | 000-003             | Divide by Zero                                | Hook    |

| 01h     | 004-007             | Single Step                                   | Hook    |

| 02h     | 008-00B             | NMI Interrupt                                 | Hook    |

| 03h     | 00C-00F             | Breakpoint                                    | Hook    |

| 04h     | 010-013             | Arithmetic Overflow                           | Hook    |

| 05h     | 014-017             | Print Screen                                  | Service |

| 06h     | 018-01B             | Low Power Hook                                | Hook    |

| 07h     | 01C-01F             | Reserved                                      | Hook    |

| 08h     | 020-023             | IRQ0, Timer0 Hardware Interrupt               | ISR     |

| 09h     | 024-027             | IRQ1, PC Compatible Keyboard Interrupt        | ISR     |

| 0Ah     | 028-02B             | IRQ2, HOPPER Miscellaneous Interrupt          | ISR     |

| 0Bh     | 02C-02F             | IRQ3, HOPPER keyboard & touch panel interrupt | Hook    |

| 0Ch     | 030-033             | IRQ4, HOPPER UART interrupt                   | Hook    |

| 0Dh     | 034-037             | IRQ5, HOPPER IR input interrupt               | ISR     |

| 0Eh     | 038-03B             | IRQ6, HOPPER XINT pin interrupt               | ISR     |

| 0Fh     | 03C-03F             | IRQ7, HOPPER RTC interrupt                    | ISR     |

| 10h     | 040-043             | Video Services                                | Service |

| 11h     | 044-047             | Equipment Check                               | Service |

| 12h     | 048-04B             | Memory Size                                   | Service |

| 13h     | 04C-04F             | Flexible Disk Services                        | Service |

| 14h     | 050-053             | Serial Port Services                          | Service |

| 15h     | 054-057             | System Functions                              | Service |

| 16h     | 058-05B             | Keyboard Services                             | Service |

| 17h     | 05C-05F             | Dummy Return                                  | -       |

| 18h     | 060-063             | Reserved                                      | -       |

| 19h     | 064-067             | Boot                                          | Service |

| 1Ah     | 068-06B             | Time-of-Day Services                          | Service |

| 1Bh     | 06C-06F             | Keyboard Break                                | Hook    |

| 1Ch     | 070-073             | Timer Tick                                    | Hook    |

| 1Dh     | 074-077             | Video Parameter Table Pointer                 | Table   |

| 1Eh     | 078-07B             | Flexible Disk Parameter Table Pointer         | Table   |

| 1Fh     | 07C-07F             | Graphics Character Table Pointer              | Table   |

| 20h-3Fh | 080-0FF             | Reserved for DOS                              | -       |

| 40h-49h | 100-127             | Reserved                                      | -       |

| 4Ah     | 128-12B             | Alarm Interrupt                               | Hook    |

| 4Bh-5Fh | 12C-17F             | Reserved                                      | -       |

| 60h-61h | 180-187             | System Manager Interrupts                     | -       |

| 62h     | 188-18B             | Reserved                                      | -       |

| 63h     | 18C-18F             | XIP Services                                  | -       |

| 64h-6Fh | 190-1BF             | Reserved                                      | -       |

| 70h     | 1C0-1C3             | Real-Time Clock Interrupt                     | ISR     |

| 71h-F0h | 1C4-3C3             | Reserved                                      | -       |

| F1h-FFh | 3C4-3FF             | Not Used                                      | -       |

Most Jaguar interrupts have the same function as the corresponding PSA interrupt. (p 28 of Phoenix

## BIOS RAM Definition

manual). Interrupts with different functions from the PSA BIOS definition are shown in the following table:

| Int<br>(Hex) | Jaguar<br>Function       | IBM-XT<br>Function | Type         | IRQ |

|--------------|--------------------------|--------------------|--------------|-----|

| 02h          | Low Batt & Module Pulled | RAM Parity Errors  | Non-Maskable | NMI |

| 06h          | Low Power Hook           | Reserved           | Hook         |     |

| 09h          | Keyboard                 | Keyboard           | Hardware*    | 1   |

| 0Ah          | Miscellaneous            | Reserved           | Hardware     | 2   |

| 0Bh          | Kbd & Touch Panel        | COM2               | Hardware     | 3   |

| 0Dh          | IR Input                 | Hard Disk          | Hardware     | 5   |

| 0Eh          | XINT pin                 | Floppy Disk        | Hardware     | 6   |

| 0Fh          | RTC                      | LPT                | Hardware     | 7   |

\*INT 9h is a hardware interrupt in the IBM XT, but it is invoked by software in Jaguar. After an INT 0Bh, software scans and debounces the keyboard and writes the keycode to the keycode register (60h). Then it invokes INT 09h.

**BIOS Data Area.** The BIOS data area is also set up by the BIOS initialization code. Jaguar RAM definitions are similar to PSA XT BIOS definitions, except as noted below.

## BIOS Data Area Definitions

| Address | Length (Bytes) | Description                                                                                                                                                                                                                                                                                                                                                                              |

|---------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 40:00h  | 8              | I/O address of up to 4 serial communications ports                                                                                                                                                                                                                                                                                                                                       |

| 40h:08h | 6              | I/O address of up to 3 parallel ports. Set to all 00s in Jaguar.                                                                                                                                                                                                                                                                                                                         |

| 40h:0Eh | 2              | Not used                                                                                                                                                                                                                                                                                                                                                                                 |

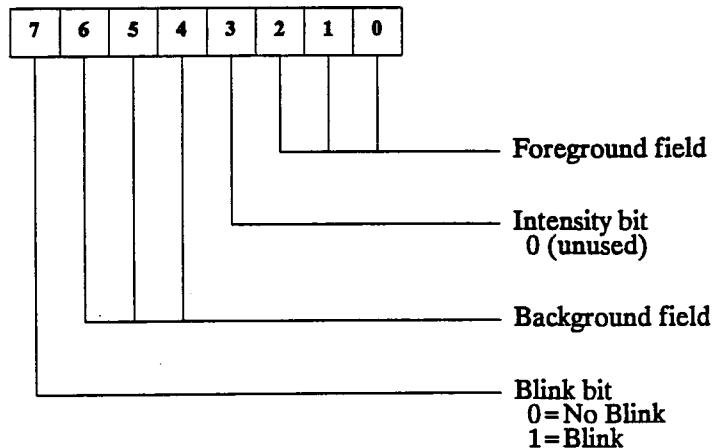

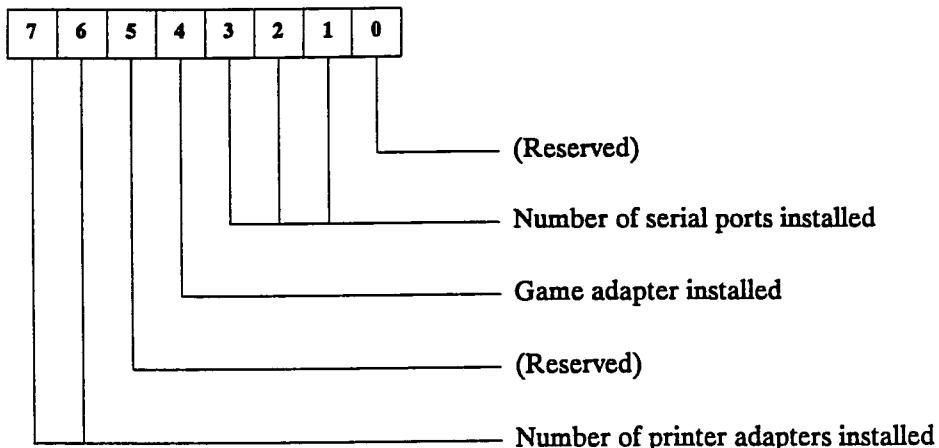

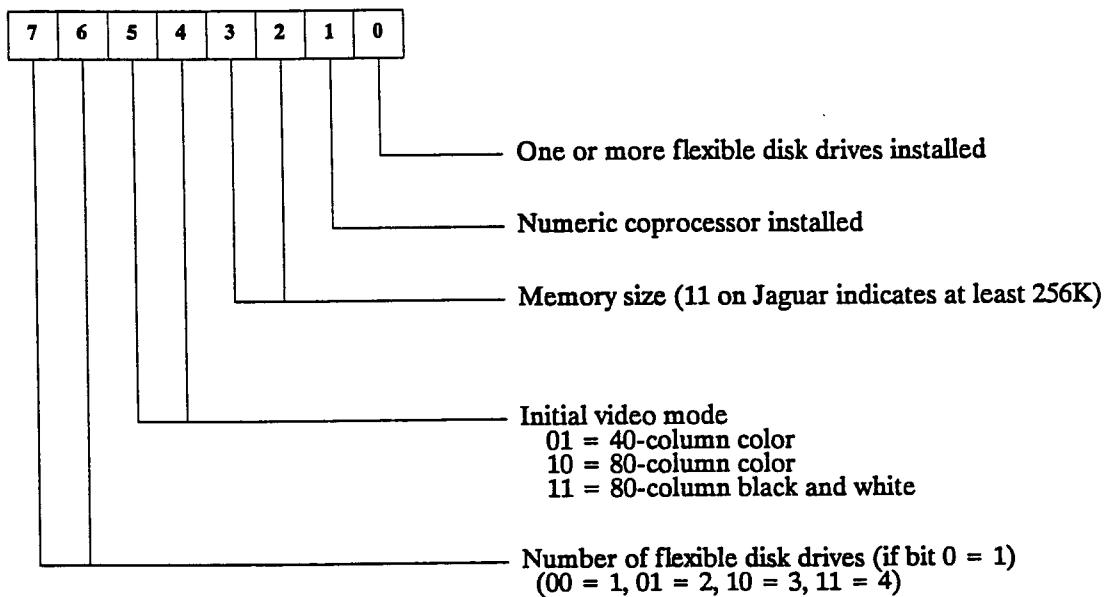

| 40h:10h | 2              | Equipment variable, where:<br>bit definition<br>15-14 Number of printer adapters<br>13-12 Reserved<br>11-9 Number of RS-232 Adapters<br>8 Reserved<br>7-6 Number of disk drives where<br>00b=1 drive<br>01b=2 drives<br>5-4 Initial video mode (11b in Jaguar)<br>3-2 Installed Memory Size (11 = at least 256k installed)<br>1 1 if Math coprocessor installed<br>0 1 if disk installed |

| 40h:12h | 1              | Reserved                                                                                                                                                                                                                                                                                                                                                                                 |

| 40h:13h | 2              | Installed memory in Kilobytes                                                                                                                                                                                                                                                                                                                                                            |

| 40h:15h | 2              | Reserved                                                                                                                                                                                                                                                                                                                                                                                 |

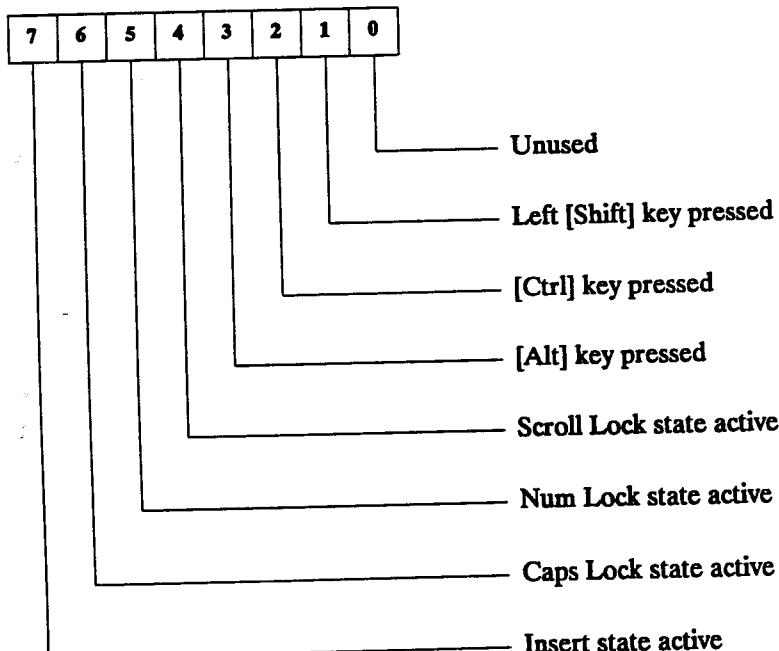

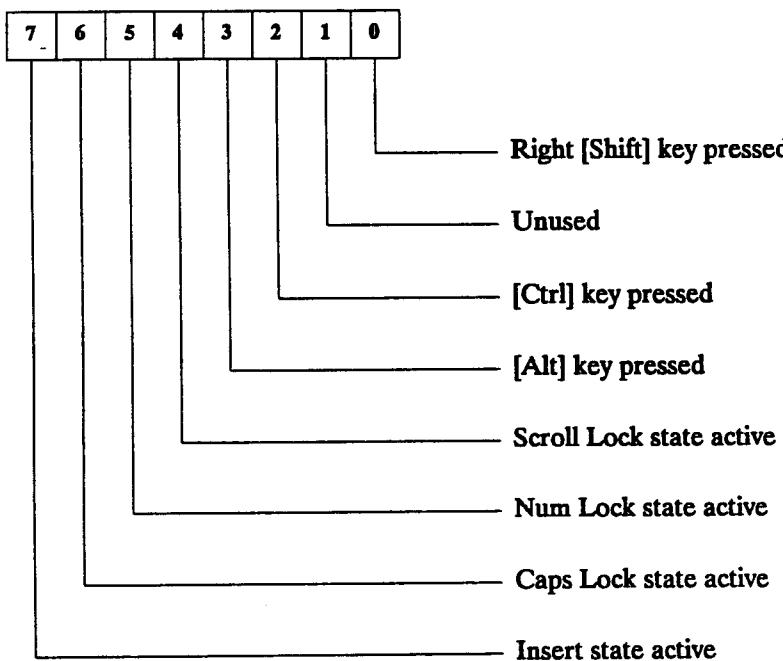

| 40h:17h | 1              | Keyboard flag 1, where:<br>bit definition<br>7 1=Insert active<br>6 1=Caps Lock active<br>5 1=Num Lock active<br>4 1=Scroll Lock active<br>3 1=Alt pressed<br>2 1=Ctrl pressed<br>1 1=Left shift pressed<br>0 1=Right shift pressed                                                                                                                                                      |

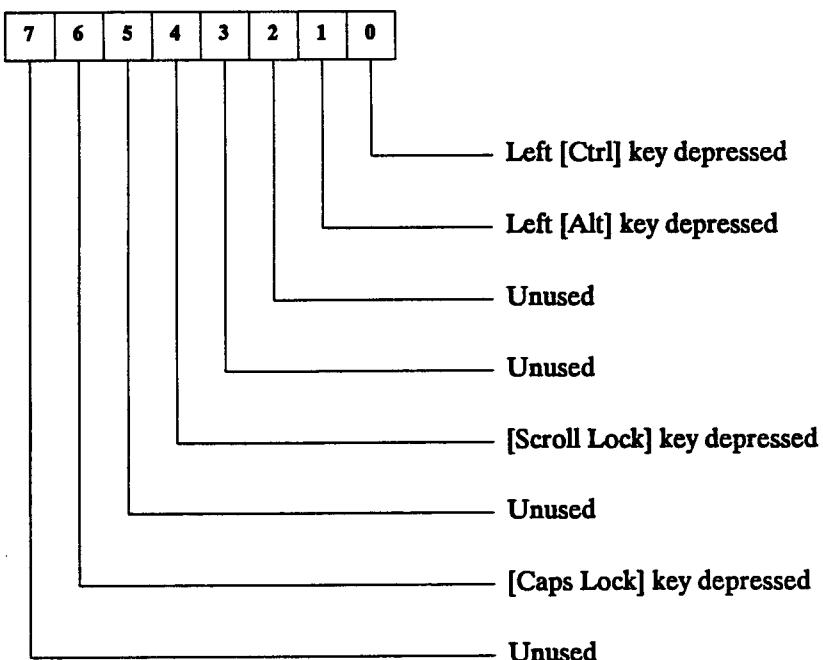

| 40h:18h | 1              | Keyboard flag 2, where:<br>bit definition<br>7 1=Insert pressed<br>6 1=Caps Lock pressed<br>5 1=Num Lock pressed<br>4 1=Scroll Lock Pressed<br>3 1=Ctrl-Num Lock state active<br>2 1=Sys Req pressed<br>1 1=Left Alt pressed<br>0 1=Left Ctrl pressed                                                                                                                                    |

| 40h:19h | 1              | Alt-key, keypad buffer                                                                                                                                                                                                                                                                                                                                                                   |

| 40h:1Ah | 2              | Key buffer read pointer                                                                                                                                                                                                                                                                                                                                                                  |

| 40h:1Ch | 2              | Key buffer write pointer                                                                                                                                                                                                                                                                                                                                                                 |

## BIOS RAM Definition

### BIOS Data Area Definitions, continued

| Address | Length (Bytes) | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|---------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 40h:1Eh | 32             | Key buffer (16 words)                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 40h:3Eh | 1              | Floppy recalibrate status (not used in Jaguar)                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 40h:3Fh | 1              | Floppy motor status (not used in Jaguar)                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 40h:40h | 1              | Floppy motor time-out count (not used in Jaguar)                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 40h:41h | 1              | Disk status return code where:<br>bit definition<br>7 1=Drive not ready<br>6 1=seek error occurred<br>5 1=disk ctrlr failed<br>4-0 Error codes, where:<br>00h=No error<br>01h=Illegal function was requested<br>02h=Address mark not found<br>03h=Write protect error<br>04h=Sector not found<br>06h=Drive door was opened<br>08h=DMA overrun error (not used in Jaguar)<br>09h=DMA boundary error (not used in Jaguar)<br>0Ch=Media type unknown<br>10h=CRC failed on disk read |

| 40h:42h | 7              | Floppy controller status and command bytes (not used in Jaguar)                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 40h:49h | 1              | Video mode setting                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 40h:4Ah | 2              | Number of columns on screen                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 40h:4Ch | 2              | Video buffer length (bytes)                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 40h:4Eh | 1              | Offset address of current display page                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 40h:50h | 16             | Cursor coordinates for 8 pages. Two bytes each page. First byte of each pair is column, second byte is row. (0,0) is upper left corner of screen.                                                                                                                                                                                                                                                                                                                                |

| 40h:60h | 2              | Cursor size. 1st byte=end scan line, 2nd byte=start scan line                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 40h:62h | 1              | Current display page number                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 40h:63h | 2              | Base I/O address of video controller                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 40h:65h | 1              | Display controller mode select register copy                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 40h:66h | 1              | Display controller palette register copy                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 40h:67h | 4              | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 40h:6Bh | 4              | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 40h:6Ch | 4              | Timer count - number of ticks since midnight                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 40h:70h | 1              | 24 hour rollover flag                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 40h:71h | 1              | Ctrl-Brk flag (bit 7=1 : <Ctrl> <Break> pressed)                                                                                                                                                                                                                                                                                                                                                                                                                                 |

## BIOS Data Area Definitions, continued

| Address | Length (Bytes) | Description                                                         |

|---------|----------------|---------------------------------------------------------------------|

| 40h:72h | 2              | Warm start flag: 1234h means warmstart                              |

| 40h:74h | 1              | Hard disk status (not used in Jaguar)                               |

| 40h:75h | 1              | Number of hard drives (set to 0 in Jaguar)                          |

| 40h:76h | 1              | Hard disk control byte copy (not used in Jaguar)                    |

| 40h:77h | 1              | Hard disk controller port offset (not used in Jaguar)               |

| 40h:78h | 3              | Parallel printer time-out table. Ports 0-2.                         |

| 40h:7Bh | 1              | Halt Value. Used for return time out count of Int 15h service 41h   |

| 40h:7Ch | 4              | Serial port time-out table. Ports 0-3. (Only port 1 used in Jaguar) |

| 40h:80h | 2              | Offset of Key buffer                                                |

| 40h:82h | 2              | Offset of first byte after key buffer                               |

| 40h:84h | 1              | Number of video rows -1 EGA mode. (not used in Jaguar)              |

| 40h:85h | 2              | Character height EGA mode. (not used in Jaguar)                     |

| 40h:87h | 1              | Video control bits EGA mode (not used in Jaguar)                    |

| 40h:88h | 1              | EGA/VGA switch data(not used in Jaguar)                             |

| 40h:89h | 1              | EGA/VGA control bits(not used in Jaguar)                            |

| 40h:8Ah | 1              | Index into DCC table VGA mode (not used in Jaguar)                  |

| 40h:8Bh | 1              | Last floppy data rate selected (not used in Jaguar)                 |

| 40h:8Ch | 1              | Hard disk controller status copy (not used in Jaguar)               |

| 40h:8Dh | 1              | Hard disk error status copy (not used in Jaguar)                    |

| 40h:8Eh | 1              | Hard disk interrupt flag (not used in Jaguar)                       |

| 40h:8Fh | 1              | Hard disk controller flag (not used in Jaguar)                      |

| 40h:90h | 2              | Floppy drive 0/1 media state (not used in Jaguar)                   |

| 40h:92h | 2              | Floppy drive 0/1 operation state (not used in Jaguar)               |

| 40h:94h | 2              | Floppy drive 0/1 track number (not used in Jaguar)                  |

| 40h:96h | 1              | Keyboard flag 3 (not used in Jaguar)                                |

## BIOS RAM Definition

### BIOS Data Area Definitions, continued

| Address | Length (Bytes) | Description                                                                                                                                                                                                        |

|---------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 40h:97h | 1              | Keyboard LED flag (not used in Jaguar)                                                                                                                                                                             |

| 40h:98h | 4              | Vector to user wait flag (not used in Jaguar)                                                                                                                                                                      |

| 40h:9Ch | 4              | User wait count (low word, high.word order) (not used in Jaguar)                                                                                                                                                   |

| 40h:A0h | 1              | Wait active flag (not used in Jaguar)                                                                                                                                                                              |

| 40h:A1h | 2              | Number of timer ticks until display timeout                                                                                                                                                                        |

| 40h:A3h | 2              | Display time out reset value.                                                                                                                                                                                      |

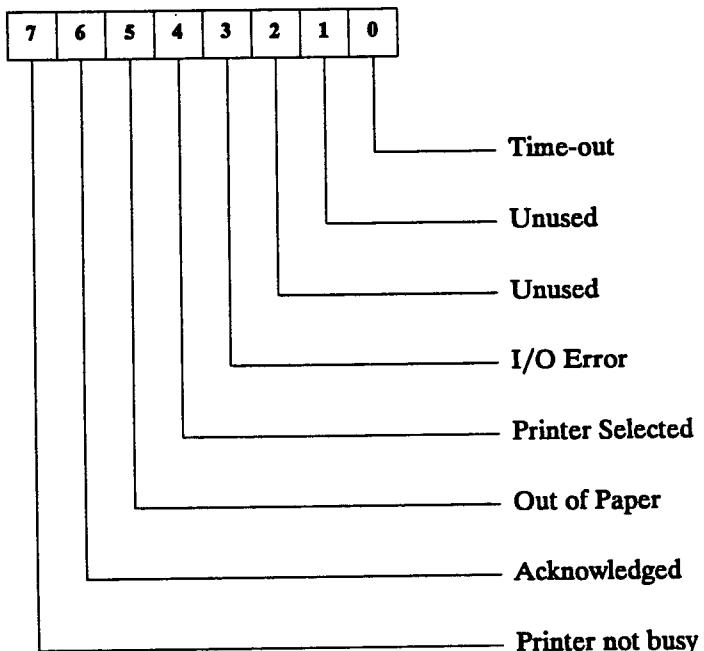

| 40h:A5h | 1              | Printer status flag                                                                                                                                                                                                |

| 40h:A6h | 1              | Cursor movement flag                                                                                                                                                                                               |

| 40h:A7h | 1              | Card Detect Register Copy                                                                                                                                                                                          |

| 40h:A8h | 4              | Pointer to table of EGA pointers (not used in Jaguar)                                                                                                                                                              |

| 40h:ACh | 2              | CPU register checksum                                                                                                                                                                                              |

| 40h:AEh | 2              | User RAM checksum                                                                                                                                                                                                  |

| 40h:B0h | 2              | Hopper register checksum                                                                                                                                                                                           |

| 40h:B2h | 2              | Stack Segment register save location                                                                                                                                                                               |

| 40h:B4h | 2              | Stack Pointer register save location                                                                                                                                                                               |

| 40h:B6h | 2              | Day Counter. This word contains the count of times the software clock at 40h:06Ch has been set to zero.                                                                                                            |

| 40h:B8h | 1              | RTC century value in bcd.                                                                                                                                                                                          |

| 40h:B9h | 1              | RTC year value in bcd                                                                                                                                                                                              |

| 40h:BAh | 1              | RTC month value in bcd                                                                                                                                                                                             |

| 40h:BBh | 1              | RTC day of month value in bcd                                                                                                                                                                                      |

| 40h:BCh | 1              | RTC hour value in bcd                                                                                                                                                                                              |

| 40h:BDh | 1              | RTC minute value in bcd                                                                                                                                                                                            |

| 40h:BEh | 1              | RTC second value in bcd                                                                                                                                                                                            |

| 40h:BFh | 1              | RTC daylight savings time flag                                                                                                                                                                                     |

| 40h:C0h | 1              | RTC alarm hour value in bcd                                                                                                                                                                                        |

| 40h:C1h | 1              | RTC alarm minute value value in bcd                                                                                                                                                                                |

| 40h:C2h | 1              | RTC alarm second value value in bcd                                                                                                                                                                                |

| 40h:C3h | 1              | RTC alarm status                                                                                                                                                                                                   |

| 40h:C6h | 1              | NCE[1] RAM FLAG where:<br>32 Indicates 2048 kbytes<br>16 Indicates 1024 kbytes<br>08 Indicates 512 kbytes<br>04 Indicates 256 kbytes<br>02 Indicates 128 kbytes<br>01 Indicates 64 kbytes<br>00 Indicates 0 kbytes |

*Machine 8/74*

## BIOS Data Area Definitions, continued

| Address  | Length (Bytes) | Description                                                                                                                                                                                                                                      |

|----------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 40h:C4h  | 2              | RTC timer value. Last value written to RTC register.                                                                                                                                                                                             |

| 40h:C7h  | 1              | NCE[2] RAM FLAG where:<br>32 indicates 2048 kbytes<br>16 indicates 1024 kbytes<br>08 indicates 512 kbytes<br>04 indicates 256 kbytes<br>02 indicates 128 kbytes<br>01 indicates 64 kbytes<br>00 indicates 0 kbytes<br>ff indicates NCE[2] is ROM |

| 40h:C8h  | 1              | Low Battery Flags                                                                                                                                                                                                                                |

| 40h:C9h  | 1              | Voltage Reference value                                                                                                                                                                                                                          |

| 40h:CAh  | 2              | Keyboard output register copy                                                                                                                                                                                                                    |

| 40h:CCh  | 1              | Port Locked & System Manager Media Changed flags where:<br>bit 7 set indicates port 1 locked<br>bit 6 set indicates port 0 locked<br>bits 2-5 unused<br>bit 1 set indicates port 1 media changed<br>bit 0 set indicates port 0 media changed     |

| 40h:CDh  | 1              | Shift annunciator flag                                                                                                                                                                                                                           |

| 40h:CEh  | 8              | Shift annunciator save location                                                                                                                                                                                                                  |

| 40h:D6h  | 1              | Unused                                                                                                                                                                                                                                           |

| 40h:D7h  | 11             | OLD BIT MAP - last bit map collected by INT 0bh                                                                                                                                                                                                  |

| 40h:E2h  | 22             | Keyboard work area                                                                                                                                                                                                                               |

| 40h:F8h  | 1              | Last key pressed                                                                                                                                                                                                                                 |

| 40h:F9h  | 1              | Key repeat counter.                                                                                                                                                                                                                              |

| 40h:FAh  | 1              | Miscellaneous Key flags.                                                                                                                                                                                                                         |

| 40h:FBh  | 1              | Mute key flags                                                                                                                                                                                                                                   |

| 40h:FCh  | 1              | Number of 33 msec ticks after key press before key repeat starts.                                                                                                                                                                                |

| 40h:FDh  | 1              | Number of 33 msec ticks between 'keys' during typematic key repeat.                                                                                                                                                                              |

| 40h:FEh  | 1              | Unused.                                                                                                                                                                                                                                          |

| 40h:100h | 1              | Print screen status byte where:<br>00h=No Print Screen activity<br>01h=Print Screen operation in progress<br>ffh=Previous Print Screen operation failed.                                                                                         |

## **Jaguar BIOS ID Block**

### **Jaguar BIOS ID Block**

The BIOS ROM contains a block of information which encodes the identification of the machine, and indicates the date the BIOS was created. The BIOS ID Block begins at FFFF:5.

FFFF:5 Date of bios release formatted as MM/DD/YY (8 bytes)

FFFF:D Unused

FFFF:E System model id (FEh for jaguar)

FFFF:F Unused

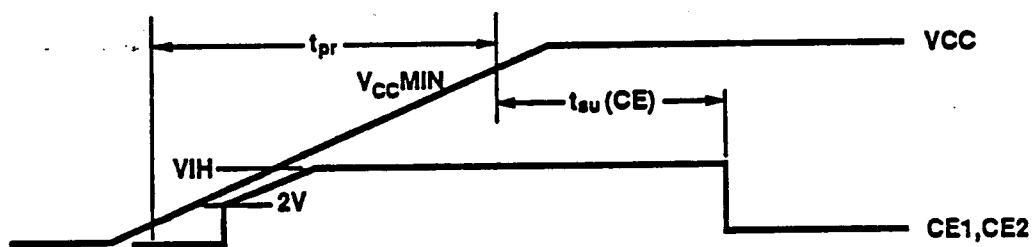

### Battery Check

There are two batteries in Jaguar: the Main battery and the Backup Battery. In addition, each RAM card has a battery.

Checks are performed on each battery to detect low voltage. If a battery has low voltage, the appropriate message is shown. The low battery messages are shown below:

- **MAIN BATTERY LOW**

- **BACKUP BATTERY LOW**

- **CARD BATTERY LOW**

#### Main Battery.

The main battery is checked at power on and once per minute while Jaguar is running. If the battery is low, the **MAIN BATTERY LOW** message is displayed each time Jaguar is powered on. Also, if the battery drops below 2.0 volts while the machine is running, the **LOW MAIN BATTERY** message is displayed the first time the voltage is found below this threshold. The thresholds for the main battery are shown below.

|           |                                    |

|-----------|------------------------------------|

| 2.5 Volts | LOW MAIN BATTERY message disabled. |

| 2.0 Volts | LOW MAIN BATTERY message enabled.  |

| 1.8 Volts | System Shutdown to backup mode.    |

In other words, the **LOW MAIN BATTERY** message is disabled until the voltage drops below 2.0 volts. Once the message is enabled, it will be displayed each time Jaguar is powered on. The message is disabled if the main battery voltage goes above 2.5 volts.

If the main battery voltage drops below 1.8 volts, the hardware causes a system shut down to backup mode.

#### Backup Battery.

The backup battery status is checked and displayed only at power on. The voltage from the backup battery is passed through a voltage divider, so the thresholds measured by the Hopper Chip are shifted downwards. The thresholds are shown below:

| TERMINAL VOLTAGE | VOLTAGE DIVIDER OUTPUT |                                      |

|------------------|------------------------|--------------------------------------|

| 3.05 Volts       | 2.77 Volts             | LOW BACKUP BATTERY message disabled. |

| 2.78 Volts       | 2.49 Volts             | LOW BACKUP BATTERY message enabled.  |

The **LOW BATTERY** message is disabled until the backup battery terminal voltage drops below 2.78 volts. Once the message is enabled, it will be displayed each time Jaguar is powered on until the terminal voltage goes above 3.05 volts.

## **Battery Check**

### **Card Battery.**

The card battery status is tested and displayed only at power on. The thresholds are shown below:

|            |                                    |

|------------|------------------------------------|

| 2.60 Volts | LOW CARD BATTERY message disabled. |

| 2.40 Volts | LOW CARD BATTERY message enabled.  |

### Power Management

Jaguar is unique among HP CMOS calculators because power to the CPU is completely shut off when the machine is turned off. This means that the CPU registers are reset to default values whenever the machine is turned on. Furthermore the CPU starts executing instructions at a different address when it is powered on, compared to where it was running when it was powered off.

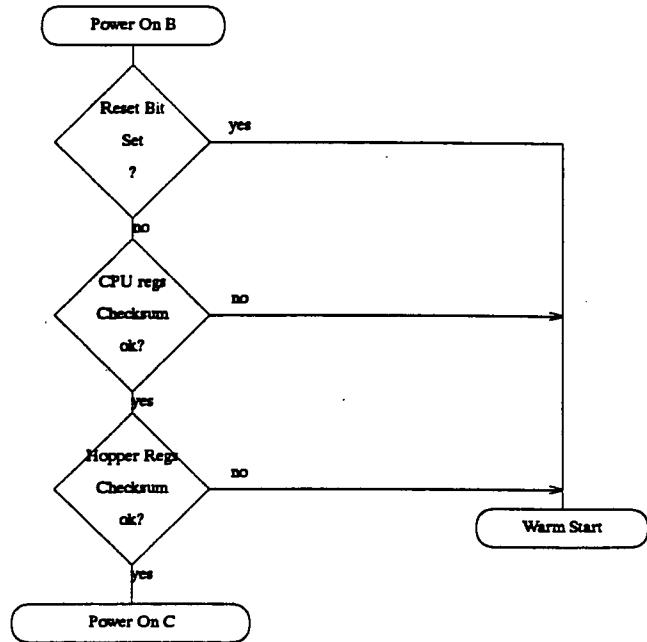

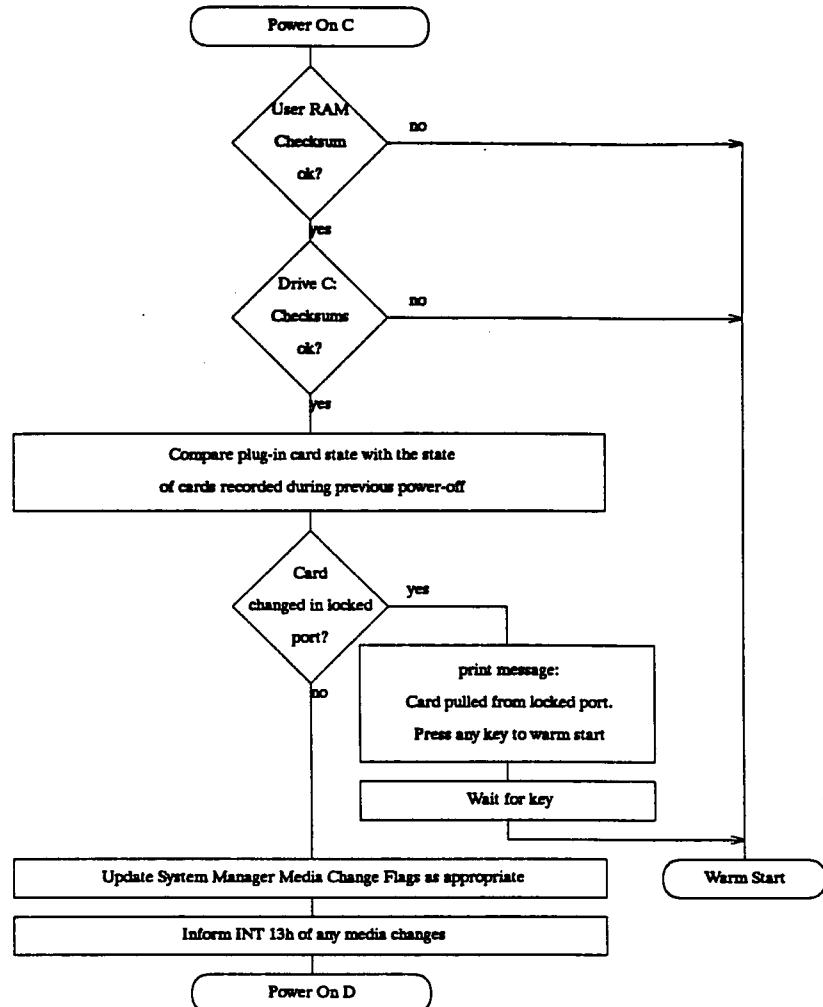

However, it is desirable from the user's viewpoint to be able to turn the machine off, then later turn it on and have it continue in the same application that was previously running. The purpose of the power management code is to perform that function. In addition, the power management code performs a number of quick checks to verify that the saved CPU registers, Hopper Memory Management registers, USER RAM and Built-In RAM DISK were not corrupted while power was off. If any of these were corrupted, the power management code will perform either a warm start or a cold start.

**Power OFF. Deep Sleep** is invoked when any of the following events occur:

- [ON] pressed when machine is ON.

- System Timer timed out because machine was idle during timeout interval.

- Very Low Battery Interrupt occurred.

- Application program invoked INT 15h function 42h.

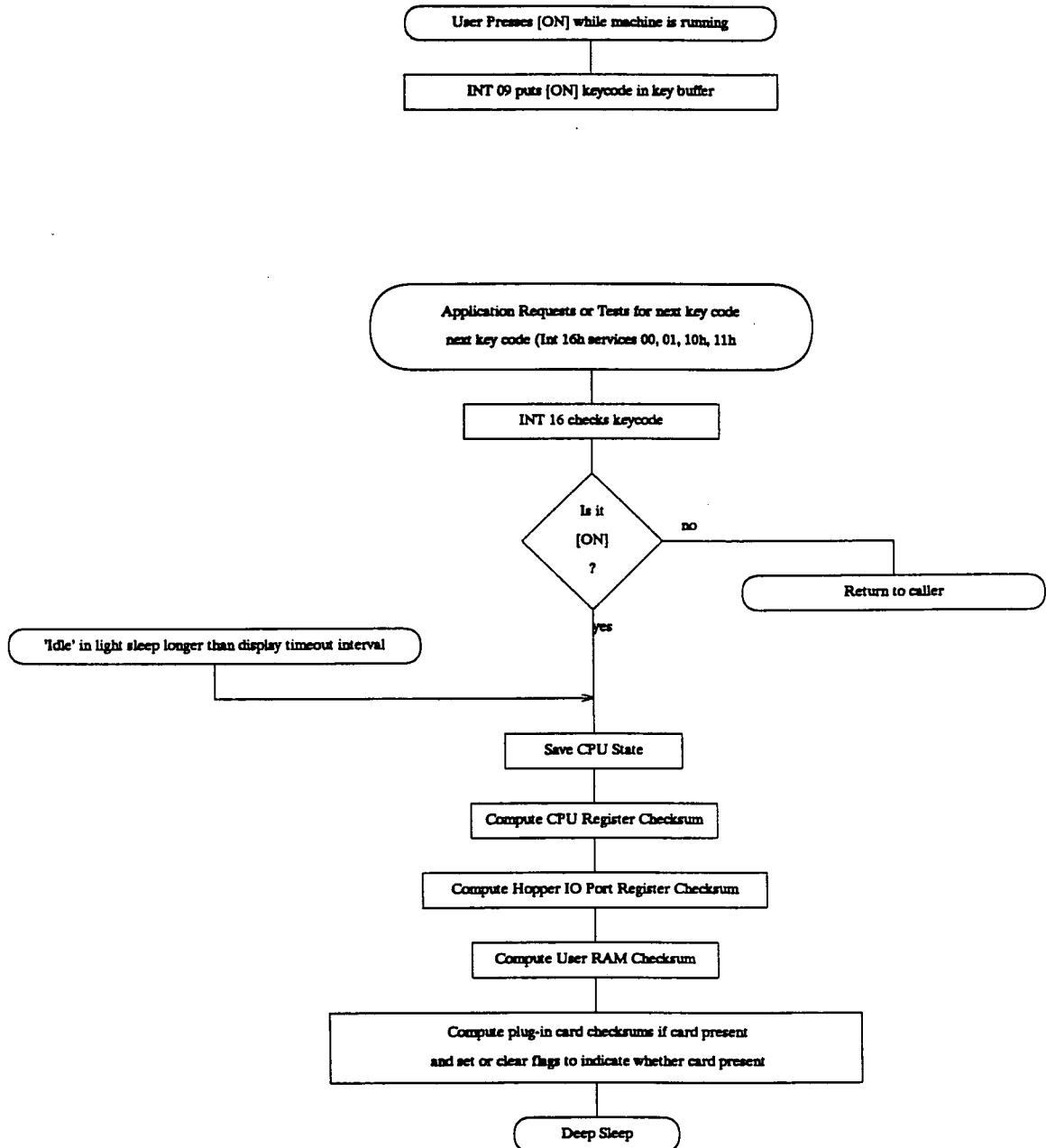

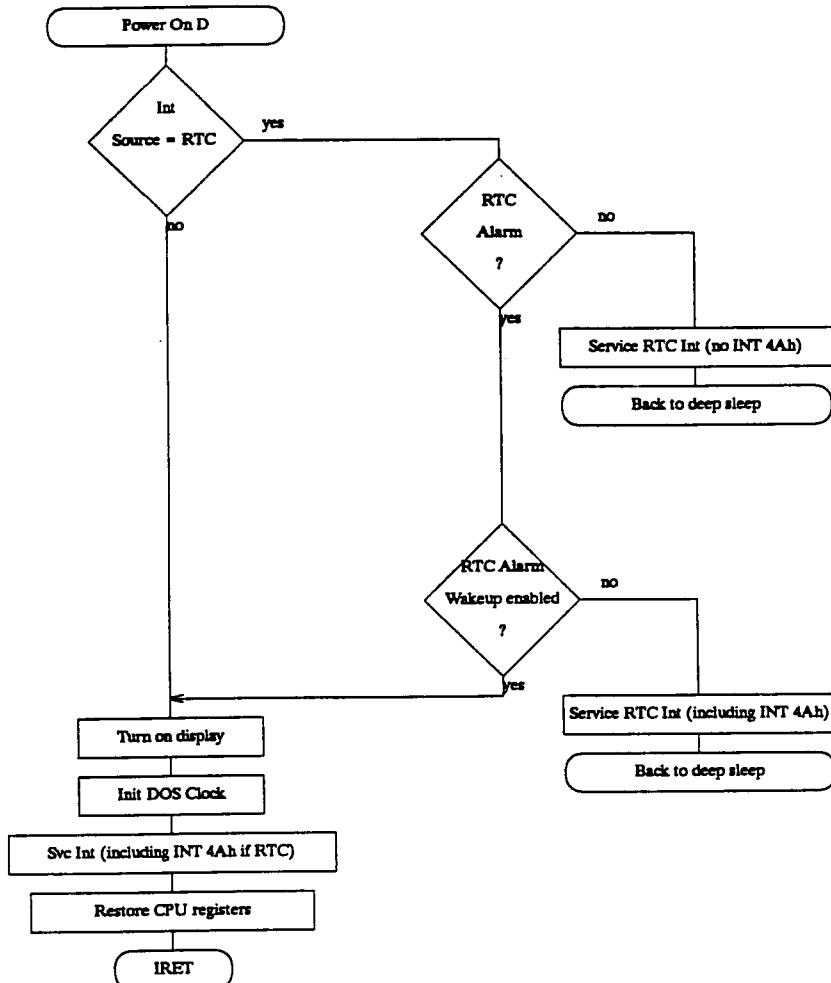

The Power Down Code behavior is described by the following flowcharts:

## Power Management

This is the normal power down sequence. All CPU registers except SS and SP are saved on the user's stack. SS and SP are saved in the BIOS data. Checksums are computed for stack area containing the CPU registers, the Hopper memory configuration registers and user RAM. These are saved for use when the machine is powered back on. The checksums of built-in RAM disk and plug-in RAM disk are computed each time the disk is written to.

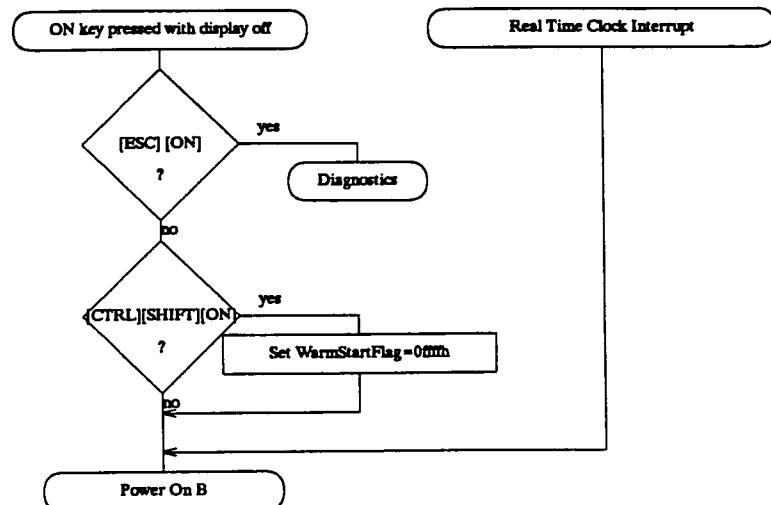

**Normal Power Up Behavior.** The code that handles power on is accessed by the reset vector (0FFFFh:0000h). This is invoked when the ON key is pressed while the machine is off.

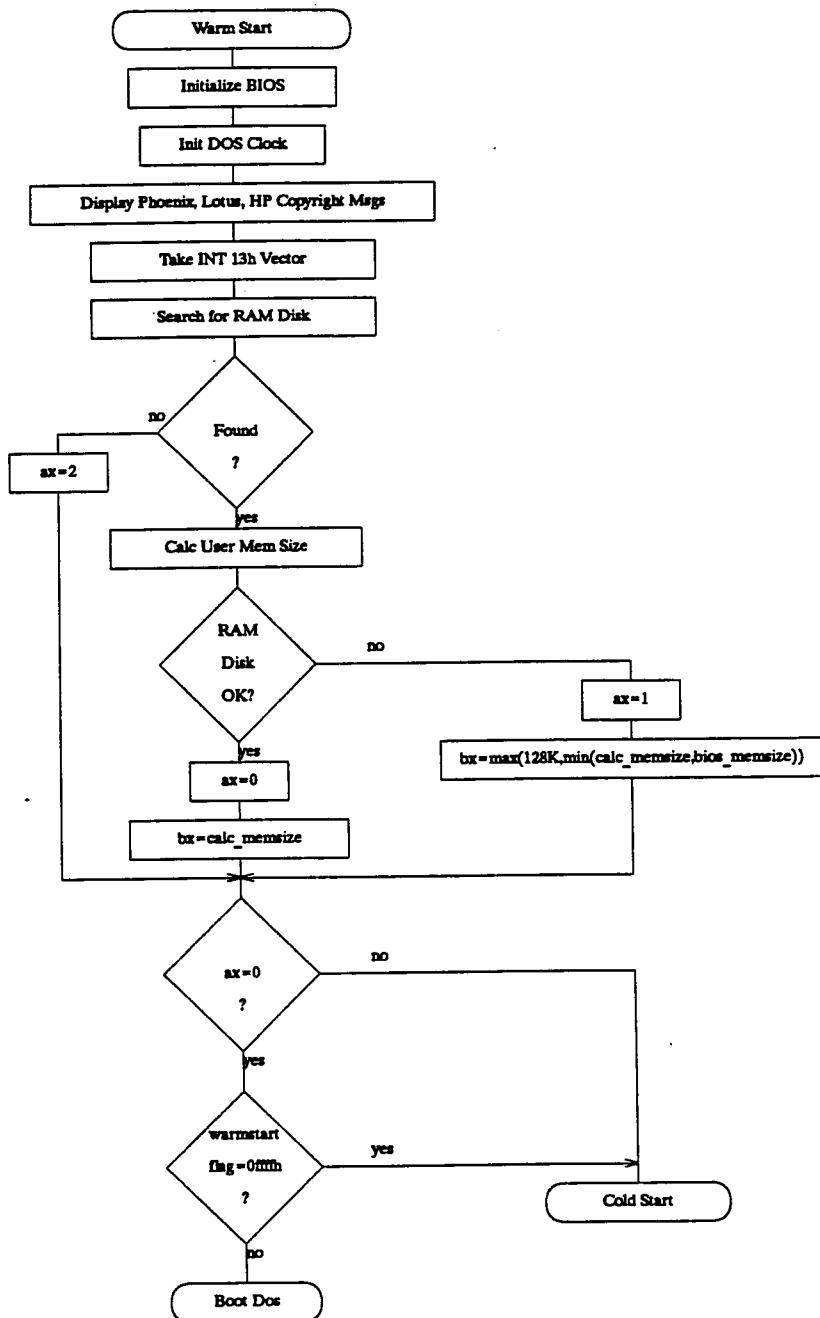

**Warm Start Behavior.** Warm Start is normally invoked by [CTRL][ALT][DEL]. It is also invoked if the user ram is found to be corrupted during normal power on initialization. It initializes User RAM, then invokes int 19h bootstrap loader.

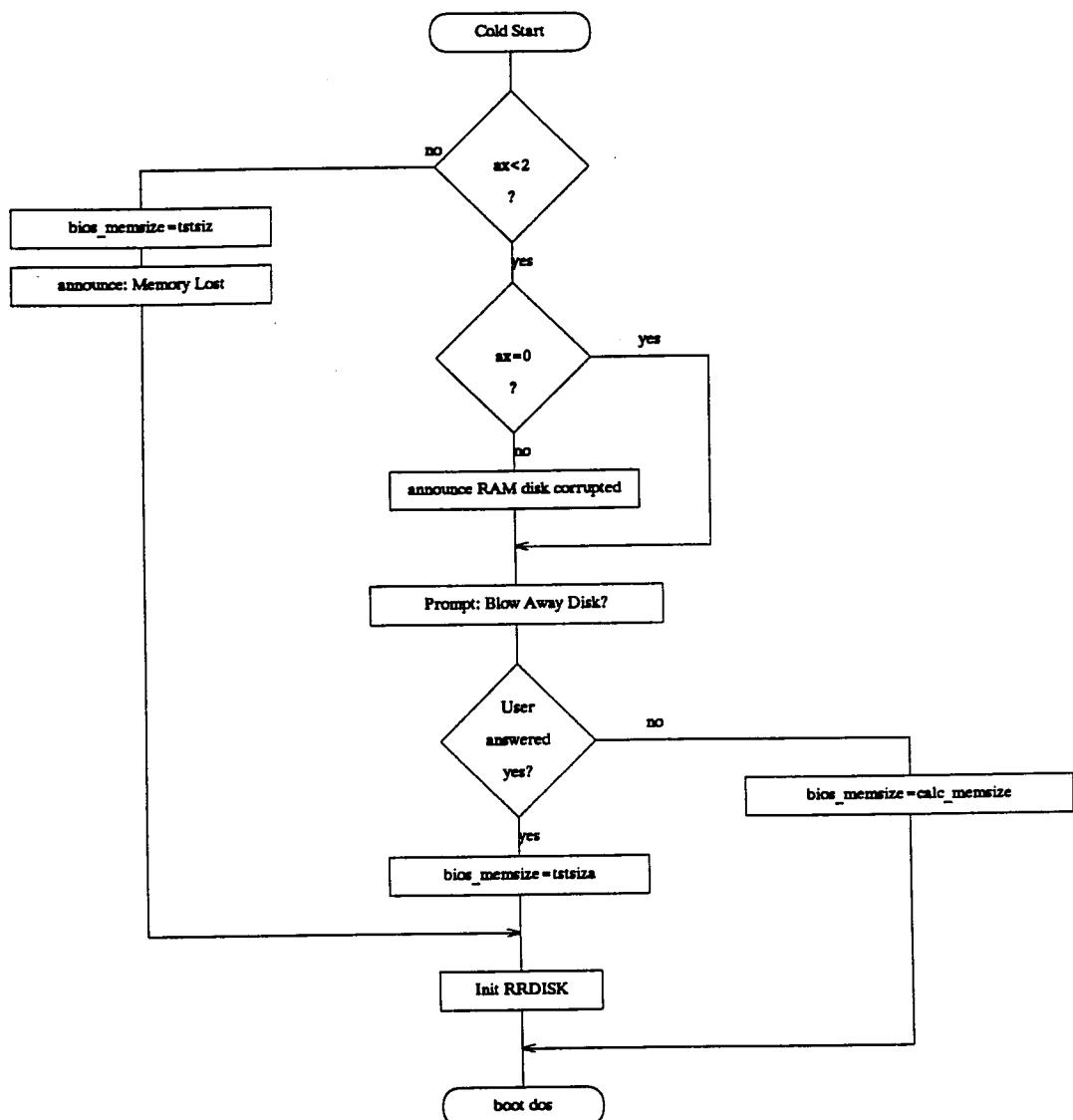

**Cold Start Behavior.** Cold Start is invoked by [Shift][CTRL][ON] or, if the Built-In RAM disk is found to be corrupted during normal power on. It initializes the User RAM and built in RAM DISK, but not the plug-in RAM DISK. The user is prompted to specify whether or not to blow away the in the built-in RAM disk. After all initializations are done, cold start invokes int 19h bootstrap loader.

**Initialization Flow Charts.** The following flow charts describe the behavior of Jaguar during Normal Power On, Warm Start and Cold Start:

## Power Management

## Power Management

## Power Management

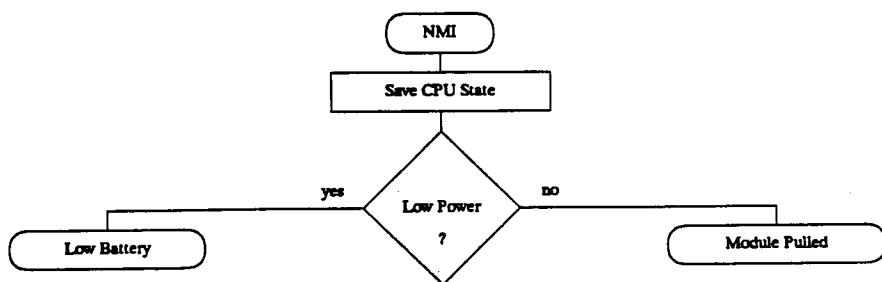

## Int 02h - Nonmaskable Interrupt

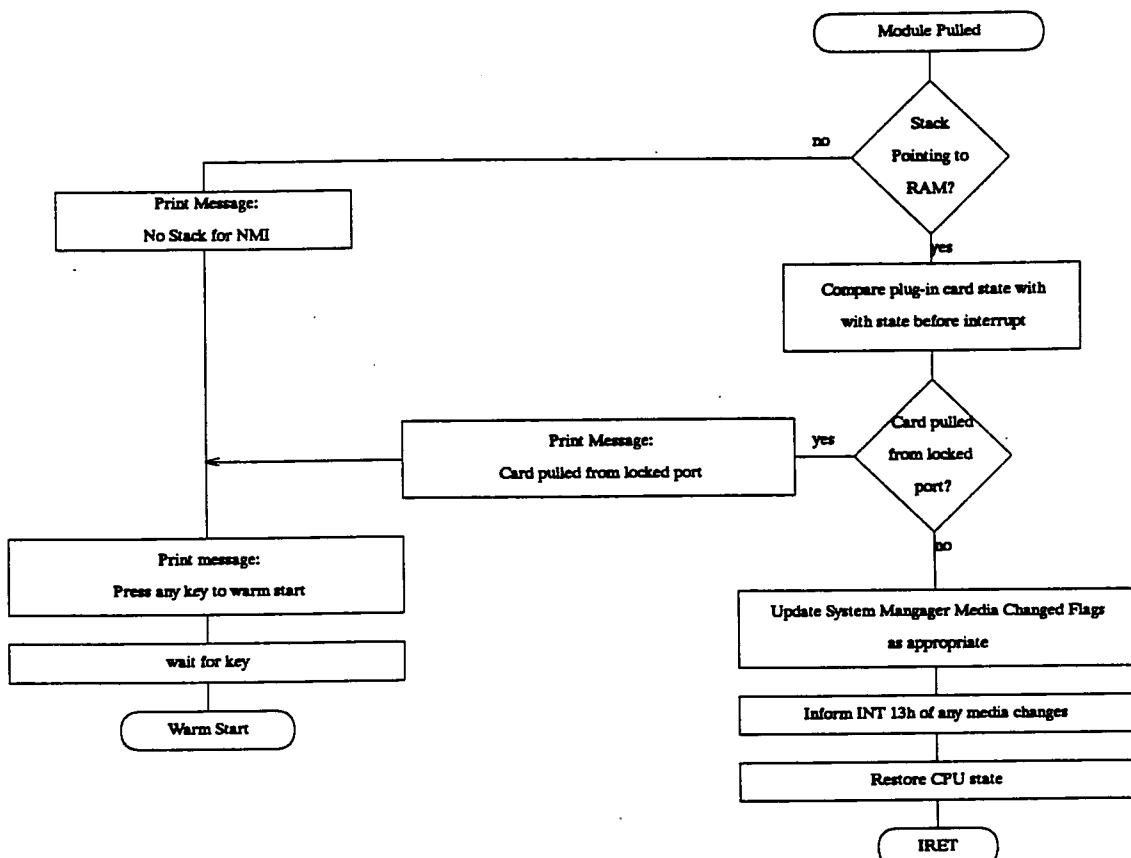

The hardware nonmaskable interrupt is invoked when either a module pulled or low battery event occurs. The Nonmaskable Interrupt routine handles these two events:

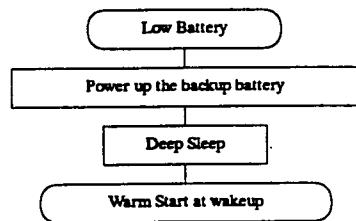

**Low Battery** If a low battery event occurs, Jaguar goes to deep sleep as quickly as possible. The checksums for User RAM, CPU registers, and hopper registers are not computed. A warm start will always occur on the next wake up after a low battery shut down.

**Module Pulled Interrupt.** The behavior of the module pulled event depends on whether the machine is in deep sleep or not. If the machine is in deep sleep, the module pulled interrupt is disabled, and the module pulled event is not detected until the next time the machine powers on. If the machine is not in deep sleep (i.e. CPU running or in light sleep), then an interrupt is generated.

The behavior of the nonmaskable interrupt code is shown in the following flow charts:

## Int 02h

## Int 05h

### Int 05h - Print Screen Interrupt

This interrupt executes the BIOS print screen function, causing the current screen contents to be written to serial printer port 0. The cursor position is saved before the operation is begun, and restored once the printout is complete. The Print Screen service routine can be initiated by either pressing the [Print Screen] key on the keyboard, or by issuing an Int 05h in a program. When executed, the Print Screen service routine updates a status byte at address 40h:100h. The value of this byte is interpreted as follows:

- 00h No Print Screen activity.

- 01h A Print Screen operation is in progress.

- FFh The previous Print Screen operation terminated with an error.

The Print Screen routine is not re-entrant. Additional Print Screen calls are ignored while a Print Screen operation is in progress. This prevents multiple screen printouts from being queued (for example, if the [Print Screen] key is quickly pressed more than once).

Print screen prints characters in the active display window. It will not print the entire contents of display memory.

### Int 06h - Low Power Hook

This interrupt is called by the system:

- Just before entering deep sleep. (AH=0).

- Just after leaving deep sleep. (AH=1). When this hook is called, the value in AL indicates the cause of the wakeup:

| AL | WAKEUP CAUSE          |

|----|-----------------------|

| 1  | ON key press          |

| 2  | UART wake up          |

| 4  | Real Time Clock Alarm |

| 8  | XINT wake up          |

- Just before entering light sleep. (AH=2).

- Just after leaving light sleep. (AH=3).

## Int 08h

### Int 08h - Timer Hardware Interrupt

A periodic hardware timer interrupt occurs on hardware interrupt level 0 (IRQ0) at a rate of 18.2 times per second. IRQ0 maps to interrupt vector 08h. The BIOS interrupt service routine for Int 08h performs several housekeeping duties for the BIOS. As part of the routine, Int 1Ch (Timer Tick) is called for each hardware timer interrupt. If an application needs a periodic interrupt, it should take over the Timer Tick interrupt hook (Int 1Ch). (The default Int 1Ch service routine is just an iret.) The application program should not attempt to take over the Int 08h service routine directly. The timer tick interrupt service routine does the following:

- Increments the BIOS software clock in the double word at 40:6C. If the count equals 1800B0h then the count at 40:6C is reset and the rollover flag at 40:70 is set to 1.

- The Timer Tick Int 1Ch is called, so that a user routine can obtain a periodic call. The default handler for Int 1C is just a dummy IRET in the BIOS.

- When control is returned from Int 1C resets the 8259 programmable interrupt controller and enables interrupts.

- The timer routine handles automatic windowing of the display. If the hardware indicates that the cursor has moved, the timer routine attempts to move the display window so it contains the cursor.

- The timer routine is decrements two counters that measure the time until display timeout (deep sleep) and the next battery measurement. However, the timer routine does not invoke either the deep sleep code or the battery measurement code. This is done by the light sleep code (Int 16h) when the display timeout timer or battery measurement timer has counted down to 0.

- The routine returns with an IRET

## Int 09h - Keyboard Translate Interrupt

Three interrupt service routines are used to input keyboard data and to process scancodes - Int 0Bh, Int 09h and Int 16h.

- Int 0Bh is invoked when a key is pressed. It performs a software scan of the keyboard and computes the scan code each time a key is pressed or released. It places the scan code in an I/O port (060h) and invokes the Int 09h service routine.

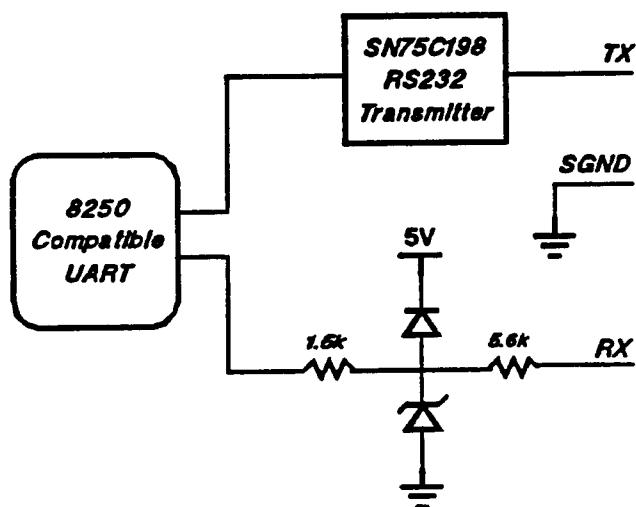

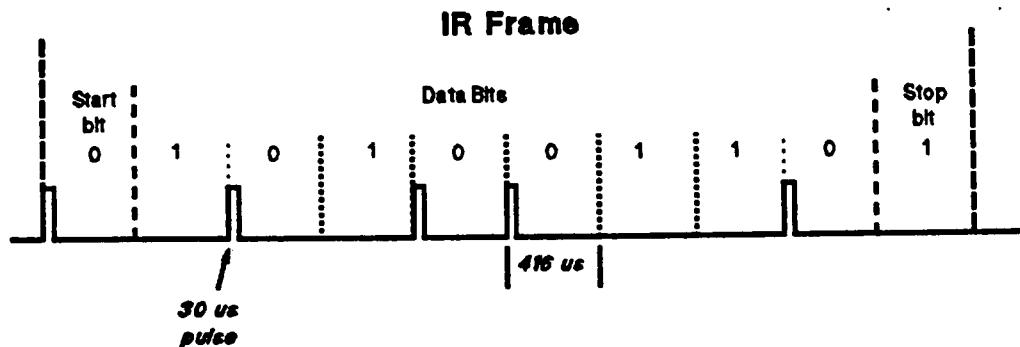

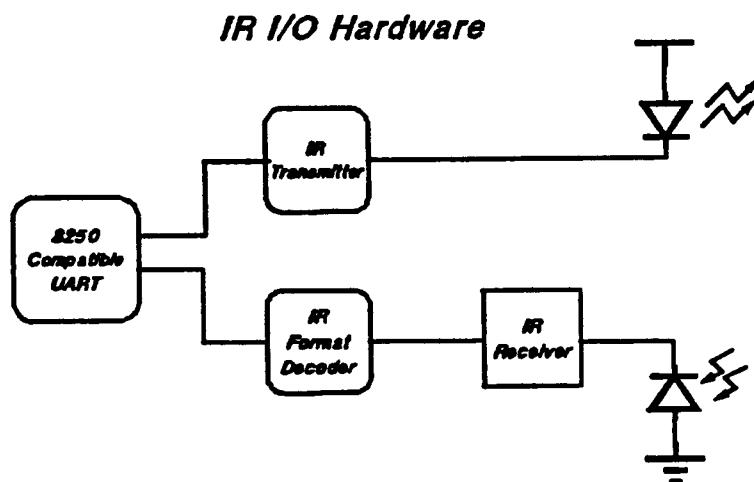

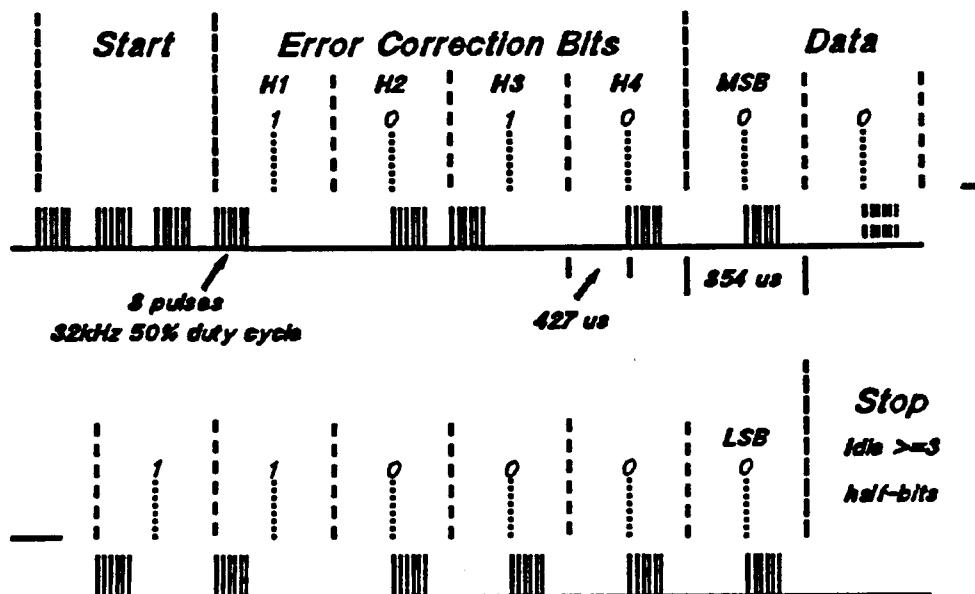

- Int 09h obtains a single byte scancode from I/O port 060h and translates it into a two-byte key code based on the state of the control, shift and alt keys. It puts the two byte code in the keybuffer.